Hardware Reference Manual 355

Intel

®

IXP2800 Network Processor

PCI Unit

The BE_DEMI bit of the PCI_CONTROL register can be set to enable big-endian on the incoming

data from the PCI Bus to both the SRAM and DRAM. The BE_DEMO bit of the PCI_CONTROL

register can be set to enable big-endian on the outgoing data to the PCI Bus from both the SRAM

and DRAM.

9.6.1 Endian for Byte Enable

During any endian conversion, PCI does not need to do any longword byte enable swapping

between two 32-bit longwords (LW1, LW0). But PCI may need to do byte enable swapping within

the 32-bit longword byte enable. Because of the different endian convention between PCI Bus and

the memory, all data going between the PCI core FIFO and memory data bus passes through the

byte lane reversal as shown in Table 138 through Table 145:

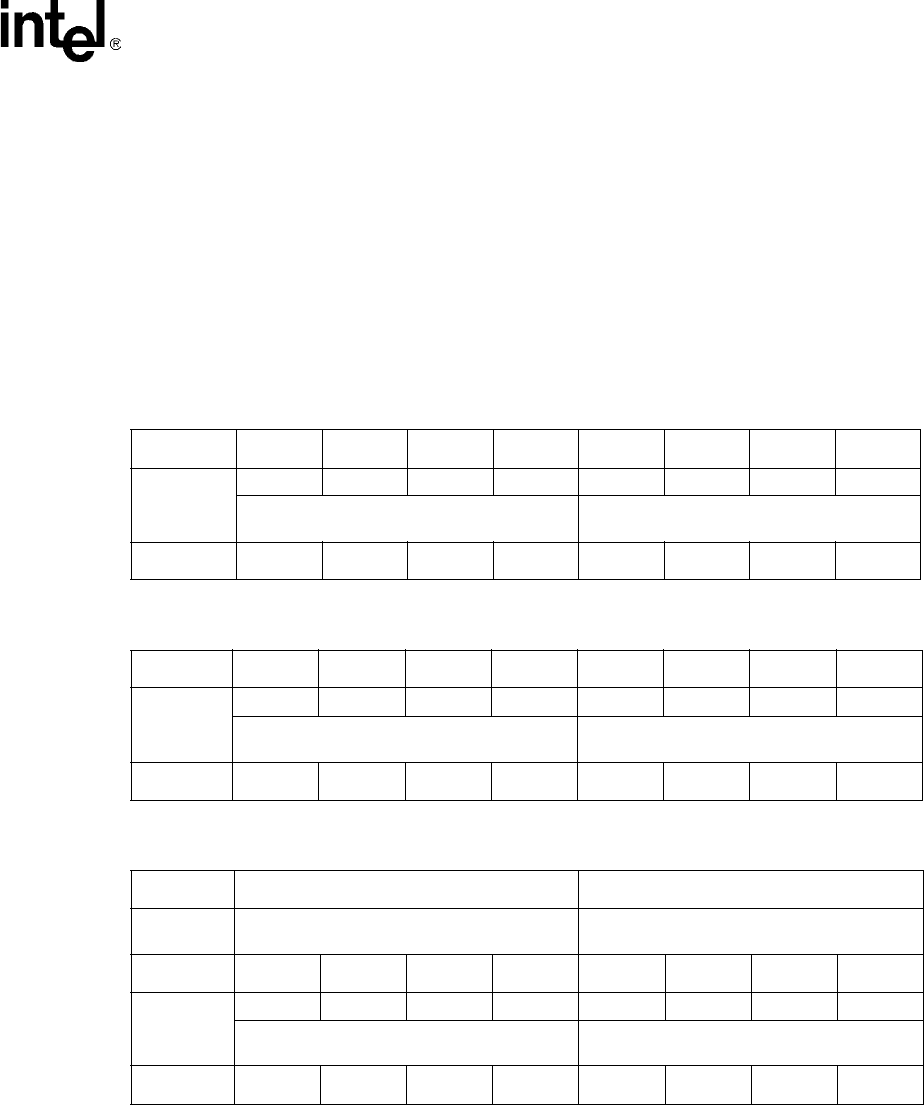

Table 138. Byte Enable Alignment for 64-Bit PCI Data In (64 Bits PCI Little-Endian to Big-

Endian with Swap)

PCI Data

IN_BE[7] IN_BE[6] IN_BE[5] IN_BE[4] IN_BE[3] IN_BE[2] IN_BE[1] IN_BE[0]

SRAM Data

OUT_BE[3] OUT_BE[2] OUT_BE[1] OUT_BE[0] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

DRAM Data

OUT_BE[4] OUT_BE[5] OUT_BE[6] OUT_BE[7] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Table 139. Byte Enable Alignment for 64-Bit PCI Data In (64 Bits PCI Big-Endian to Big-Endian

without Swap)

PCI Data

IN_BE[4] IN_BE[5] IN_BE[6] IN_BE[7] IN_BE[0] IN_BE[1] IN_BE[2] IN_BE[3]

SRAM Data

OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

DRAM Data

OUT_BE[4] OUT_BE[5] OUT_BE[6] OUT_BE[7] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Table 140. Byte Enable Alignment for 32-Bit PCI Data In (32 bits PCI Little-Endian to Big-

Endian with Swap)

PCI Add[2]=1 PCI Add[2]=0

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

PCI Data

IN_BE[3] IN_BE[2] IN_BE[1] IN_BE[0] IN_BE[3] IN_BE[2] IN_BE[1] IN_BE[0]

SRAM Data

OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

DRAM Data

OUT_BE[4] OUT_BE[5] OUT_BE[6] OUT_BE[7] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]