274 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.3.5.2 CSIX

8.3.5.2.1 Horizontal Parity

The transmit logic computes odd Horizontal Parity for each transmitted 16-bits of each Cword, and

transmits it on TxPar.

8.3.5.2.2 Vertical Parity

The transmit logic computes Vertical Parity on CFrames. There is a 16-bit VP Accumulator

register. At the beginning of each CFrame, the register is cleared. As each Cword is transmitted,

odd parity is accumulated in the register as defined in the CSIX specification (16 bits of vertical

parity are formed on 32 bits of transmitted data by treating the data as words; i.e., bit 0 and bit 16 of

the data are accumulated into parity bit 0, bit 1, and bit 17 of the data are accumulated into parity

bit 1, etc.). The accumulated value is transmitted in the Cword along with the last byte of Payload

and any padding, if required.

8.4 RBUF and TBUF Summary

Table 102 summarizes and contrasts the RBUF and TBUF operations.

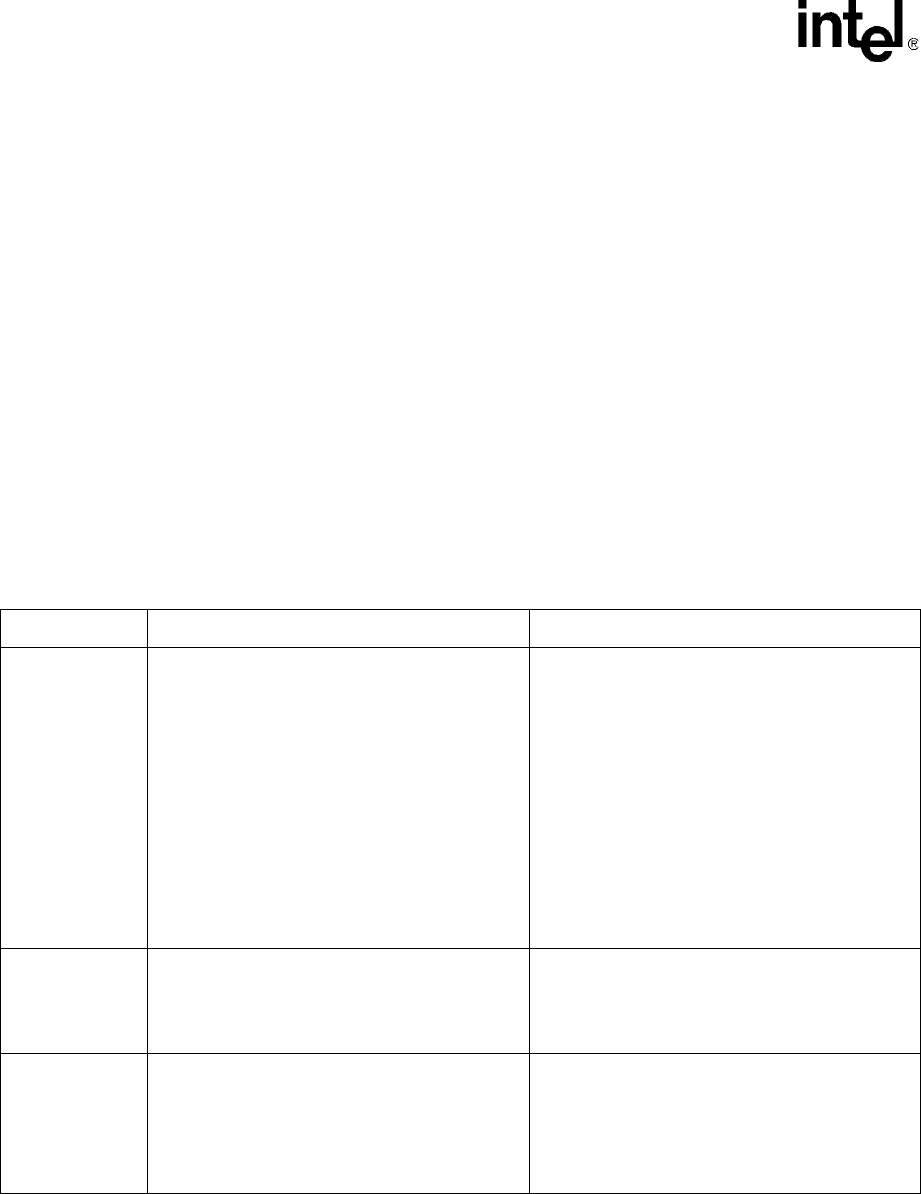

Table 102. Summary of RBUF and TBUF Operations (Sheet 1 of 2)

Operation RBUF TBUF

Allocate element

SPI-4

Hardware allocates an element upon receipt of a

non-idle Control Word, or when a previous element

becomes full and another Data Word arrives with no

intervening Control Word. Any available element in

the SPI-4 partition may be allocated, however,

elements are guaranteed to be handed to threads in

the order in which they arrive.

CSIX

Hardware allocates an element upon receipt of

RxSof asserted. Any available element in the CSIX

Control or CSIX Data partition may be allocated

(according to the type), however, elements are

guaranteed to be handed to threads in the order in

which they arrive.

Microengine allocates an element. Because the

elements are transmitted in FIFO order (within each

TBUF partition), the Microengine can keep the

number of the next element in software.

Fill element

SPI-4

Hardware fills the element with Data Words.

CSIX

Hardware fills the element with Payload.

Microcode fills the element from DRAM using the

dram[tbuf_wr] instruction and from Microengine

registers using msf[write] instruction.

Set element valid

SPI-4

Set valid by hardware when either it becomes full or

when a Control Word is received.

CSIX

Set valid by hardware when the number of bytes in

Payload Length have been received.

The element’s Transmit Valid bit is set. This is done

by a write to the TBUF_Element_Control_$_# CSR

($is A or B, # is the element number).