172 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Microengines

Typically, the external units access the Transfer registers in response to commands sent by the

Microengines. The commands are sent in response to instructions executed by the Microengine

(for example, the command instructs a SRAM controller to read from external SRAM, and place

the data into a S_TRANSFER_IN register). However, it is possible for an external unit to access a

given Microengine’s Transfer registers either autonomously, or under control of a different

Microengine, or the Intel XScale

®

core, etc. The Microengine interface signals controlling writing/

reading of the Transfer_In/Transfer_Out registers are independent of the operation of the rest of the

Microengine.

4.1.3.3 Next Neighbor Registers

A new feature added for the Microengine Version 2 are 128 Next Neighbor registers that provide a

dedicated datapath for transferring data from the previous/next neighbor Microengine. Next

Neighbor registers, when used as a source in an instruction, supply operands to the execution

datapath. They are written in two different ways: (1) by an external entity, typically, but not limited

to, another adjacent Microengine, or (2) by the same Microengine they are in, as controlled by

CTX_Enable[NN_Mode]. The specific register is selected in one of two ways: (1) Context-

relative, the register number is encoded in the instruction, or (2) as a Ring, selected via NN_Get

and NN_Put CSR registers.

When CTX_Enable[NN_Mode] is ‘0’ – When Next Neighbor is used as a destination in an

instruction, the instruction result data is sent out of the Microengine, typically to another, adjacent

Microengine.

When CTX_Enable[NN_Mode] is ‘1’– When Next Neighbor is used as a destination in an

instruction, the instruction result data is written to the selected Next Neighbor register in the

Microengine. Note that there is a 5-instruction latency until the newly written data can be read.

The data is not sent out of the Microengine as it would be when CTX_Enable[NN_Mode] is ‘0’.

4.1.3.4 Local Memory

Local Memory is addressable storage located in the Microengine, organized as 640 32-bit words.

Local Memory is read and written exclusively under program control. Local Memory supplies

operands to the execution datapath as a source, and receives results as a destination.

The specific Local Memory location selected is based on the value in one of the Local

Memory_Addr registers, which are written by local_CSR_wr instructions. There are two

LM_Addr registers per Context and a working copy of each. When a Context goes to the Sleep

state, the value of the working copies is put into the Context’s copy of LM_Addr. When the

Context goes to the Executing state, the value in its copy of LM_Addr is put into the working

copies. The choice of LM_Addr_0 or LM_Addr_1 is selected in the instruction.

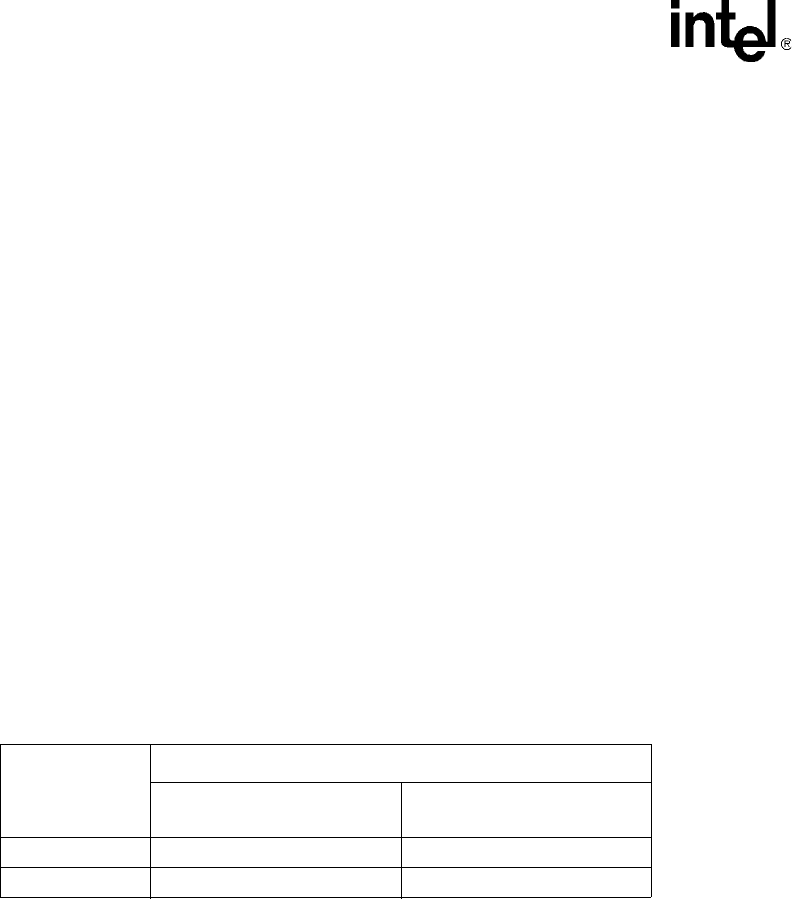

Table 56. Next Neighbor Write as a Function of CTX_Enable[NN_Mode]

NN_Mode

Where the Write Goes

External?

NN Register in this

Microengine?

0Yes No

1No Yes