168 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Microengines

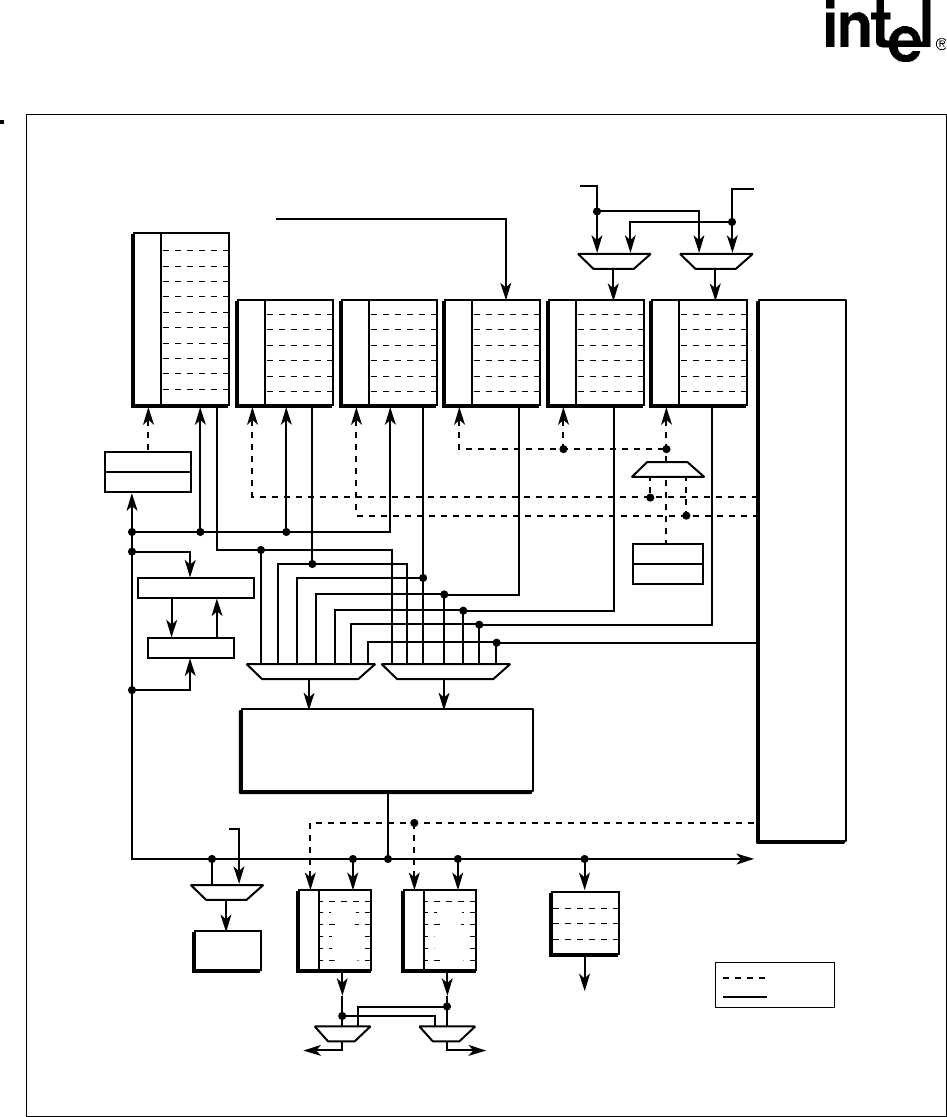

Figure 56. Microengine Block Diagram

B1670-01

128

GPRs

(A Bank)

d

e

c

o

d

e

128

GPRs

(B Bank)

128

Next

Neighbor

128

D

XFER

In

NNData_In

(from previous ME)

D_Push

(from DRAM)

S_Push

(from SRAM

Scratchpad,

MSF, Hash,

PCI, CAP)

128

S

XFER

In

640

Local

Mem

A_Src

B_Src

Immed

NN_Data_Out

(to next ME)

Dest

Control

Store

Lm_addr_1

Lm_addr_0

CRC_Remainder

A_Operand

B_Operand

ALU_Out

S_Push

S_PullD_Pull

CRC Unit

Local

CSRs

T_Index

NN_Get

Execution

Datapath

(Shift, Add, Subtract, Multiply Logicals,

Find First Bit, CAM)

Command

CMD

FIFO

(4)

Control

Data

128

D

XFER

Out

128

S

XFER

Out