420 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.4.6.24 SRAM CH3 Events Target ID(001011) / Design Block #(0010)

45 spl_s1_enq_cmd_wph P_CLK single separate

SRAM1 Pull Command Queue FIFO

Enqueue

46 spl_s1_deq_wph P_CLK single separate

SRAM1 Pull Command Queue FIFO

Dequeue

47 spl_s1_cmd_que_full_wph P_CLK Long separate SRAM1 Pull Command Queue FIFO Full

48 spl_s2_cmd_valid_rph P_CLK Long separate SRAM2 Pull Command Queue FIFO Valid

49 spl_s2_enq_cmd_wph P_CLK single separate

SRAM2 Pull Command Queue FIFO

Enqueue

50 spl_s2_deq_wph P_CLK single separate

SRAM2 Pull Command Queue FIFO

Dequeue

51 spl_s2_cmd_que_full_wph P_CLK Long separate SRAM2 Pull Command Queue FIFO Full

52 spl_s3_cmd_valid_rph P_CLK Long separate SRAM3 Pull Command Queue FIFO Valid

53 spl_s3_enq_cmd_wph P_CLK single separate

SRAM3 Pull Command Queue FIFO

Enqueue

54 spl_s3_deq_wph P_CLK single separate

SRAM3 Pull Command Queue FIFO

Dequeue

55 spl_s3_cmd_que_full_wph P_CLK Long separate SRAM3 Pull Command Queue FIFO Full

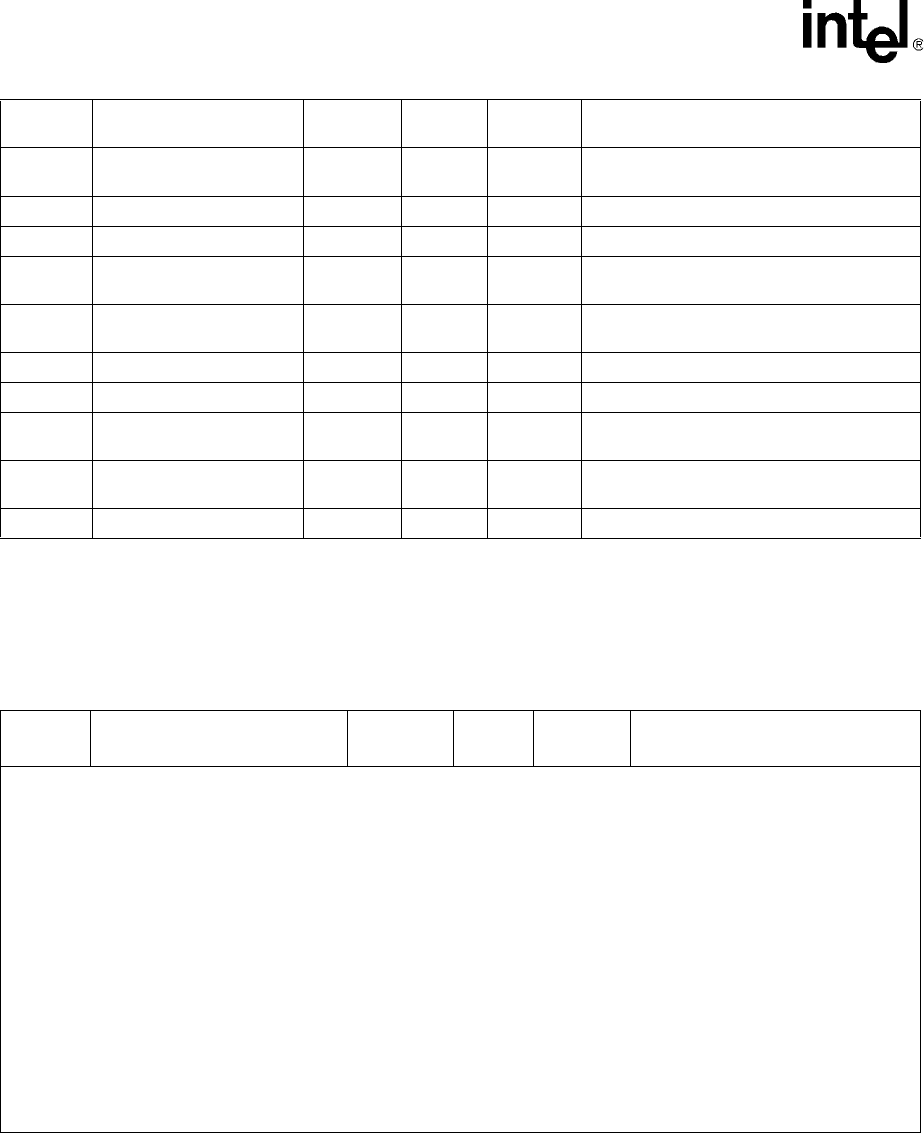

Table 177. SRAM DP0 PMU Event List (Sheet 3 of 3)

Table 178. SRAM CH3 PMU Event List

Event

Number

Event Name

Clock

Domain

Pulse/

Level

Burst Description

Note:

1. All the SRAM Channel has same event lists.

2. S_CLK = SRAM clock domain

3. P_CLK = PP clock domain

signals that begin with sps_ correspond to S_Push Arb

signals that begin with spl_ correspond to S_Pull Arb

signals that contain _pc_ (after the unit designation) correspond to the PCI target interface

signals that contain _m_ (after the unit designation) correspond to the MSF target interface

signals that contain _sh_ (after the unit designation) correspond to the SHaC target interface

signals that contain _s0_ (after the unit designation) correspond to the SRAM0 target interface

signals that contain _s1_ (after the unit designation) correspond to the SRAM1 target interface

signals that contain _s2_ (after the unit designation) correspond to the SRAM2 target interface

signals that contain _s3_ (after the unit designation) correspond to the SRAM3 target interface