Hardware Reference Manual 135

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.12.1.1 Data Transfers

The current rate for data transfers is four bytes, except for the Slowport. The 8-bit and 16-bit

accesses are only available in the Slowport bus. The devices connected to the Slowport dictate this

data width. The user has to configure the data width register resident in the Slowport to run a

different type of data transaction. There is no burst to Slowport.

3.12.1.2 Data Alignment

For all the CSR accesses, a 32-bit data bus is assumed. Therefore, the lower two bits of the address

bus are ignored.

For the Slowport accesses, 8-, 16-, or 32-bit data access is dictated by the external device

connected to the Slowport. The APB Bus should be able to match the data width according to

which devices it is talking to.

SeeTable 52 for additional details on data alignment.

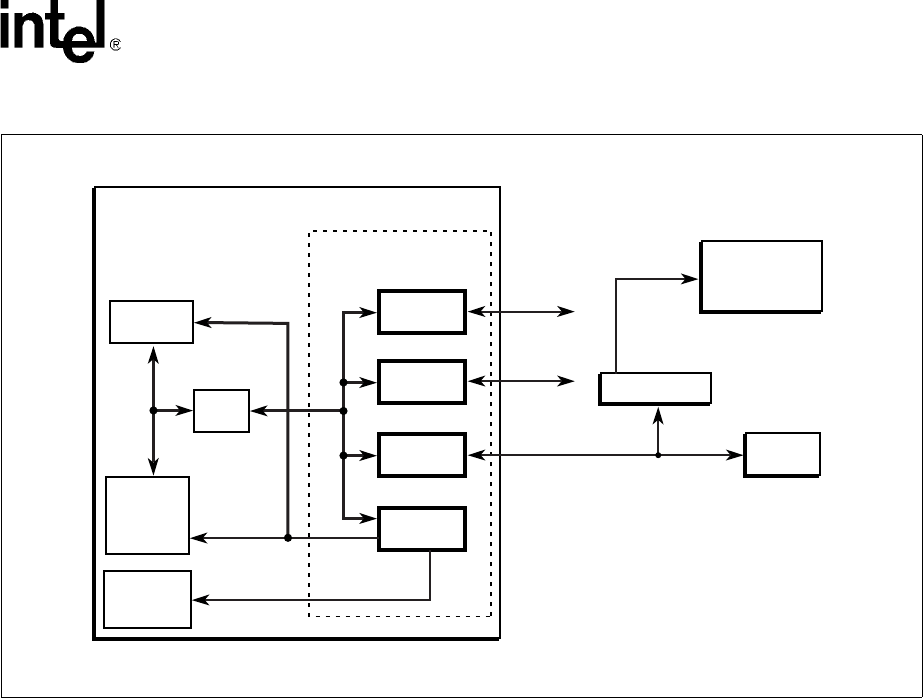

Figure 30. XPI Interfaces for IXP2800 Network Processor

B1740-02

PCI

SHaC

Timer

CPP Bus

APB Bus [31:0]

SlowPort

GPIO

UART

watchdog_reset

[3:0]

PROM

SONET/SDH

Microprocessor

Interface

Demultiplexor

Intel

®

IXP2400/2800

Network Processor

XPI

[7:0]

[7:0]

rx,tx

[7:0]/[15:0]/[31:0]

Reset

Sequential

Logic

Intel

XScale

®

Core