342 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

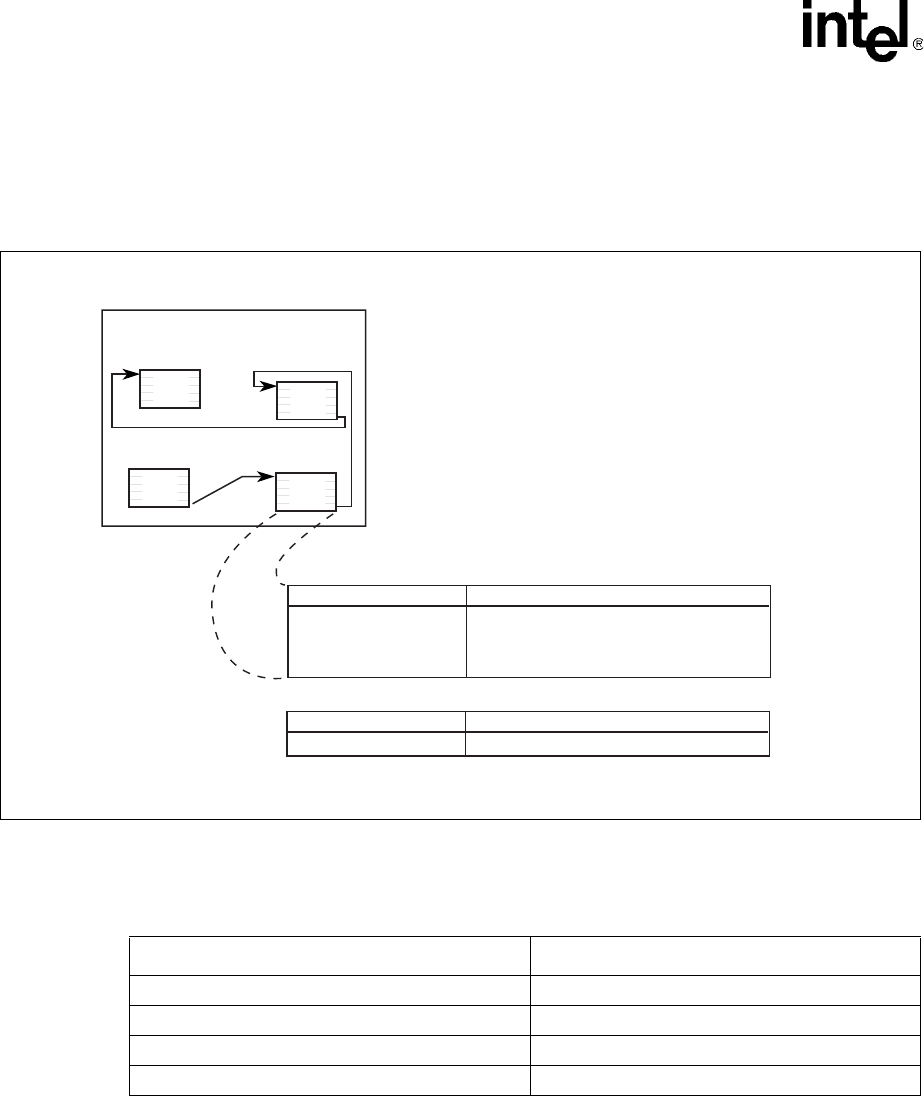

9.4.1.3 DMA Descriptor

Each descriptor occupies four 32-bit Dwords and is aligned on a 16-byte boundary. The DMA

channels read the descriptors from local SRAM into the four DMA working registers once the

control register has been set to initiate the transaction. This control must be set explicitly. This

starts the DMA transfer. The register names for the DMA channels are listed in Figure 127.

After a descriptor is processed, the next descriptor is loaded in the working registers. This process

repeats until the chain of descriptors is terminated (i.e., the End of Chain bit is set). See Table 126.

Figure 127. DMA Descriptor Reads

A9774-01

Local SRAM

4

3

1

2

Last

Descriptor

Next

Descriptor

Prior

Descriptor

Current

Descriptor

Working Register

Control Register

Byte Count Register CHAN_X_BYTE_COUNT

PCI Address Register CHAN_X_PCI_ADDR

DRAM Address Register CHAN_X_DRAM_ADDR

Descriptor Pointer Register CHAN_S_DESC_PTR

Channel Register Name (X can be 1, 2, or 3)DMA Channel Register

Control Register CHAN_X_CONTROL

Channel Register Name (X can be 1, 2, or 3)DMA Channel Register

Table 126. DMA Descriptor Format

Offset from Descriptor Pointer Description

0x0 Byte Count

0x4 PCI Address

0x8 DRAM Address

0xC Next Descriptor Address