Hardware Reference Manual 123

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

32-Bit (Longword) Read

32-bit (longword) reads are independent of endianness. Byte lane 0 from the Intel XScale

®

core’s

data bus gets into the byte 0 location of the read register inside the Intel XScale

®

core, byte lane 1

from the Intel XScale

®

core’s data bus gets into the byte 1 location of the read register inside the

Intel XScale

®

core, etc. The software determines byte location, based on the endian setting.

3.10.1.1.2 The Intel XScale

®

Core Writing to the IXP2800

Network Processor

Writes by the Intel XScale

®

core can also be divided into the following three categories:

• Byte Write

• Word Write (16 bits)

• Longword write (32 bits)

Byte Write

When the Intel XScale

®

core writes a single byte to external memory, it puts the byte in the byte

lane where it intends to write it, along with the byte enable for that byte turned ON, based on the

endian setting of the system. Intel XScale

®

core register bits [7:0] always contain the byte to be

written, regardless of the B-bit setting.

For example, if the Intel XScale

®

core wants to write to byte 0 in the little-endian system, it puts

the byte in byte lane 0 and turns X_BE[0] to ON. If the system is big-endian, the Intel XScale

®

core puts byte 0 in byte lane 3 and turns X_BE[3] to ON. Other possible combinations of byte lanes

and byte enables are shown in the Table 47. Byte lanes other than the one currently being driven by

the Intel XScale

®

core, contain undefined data.

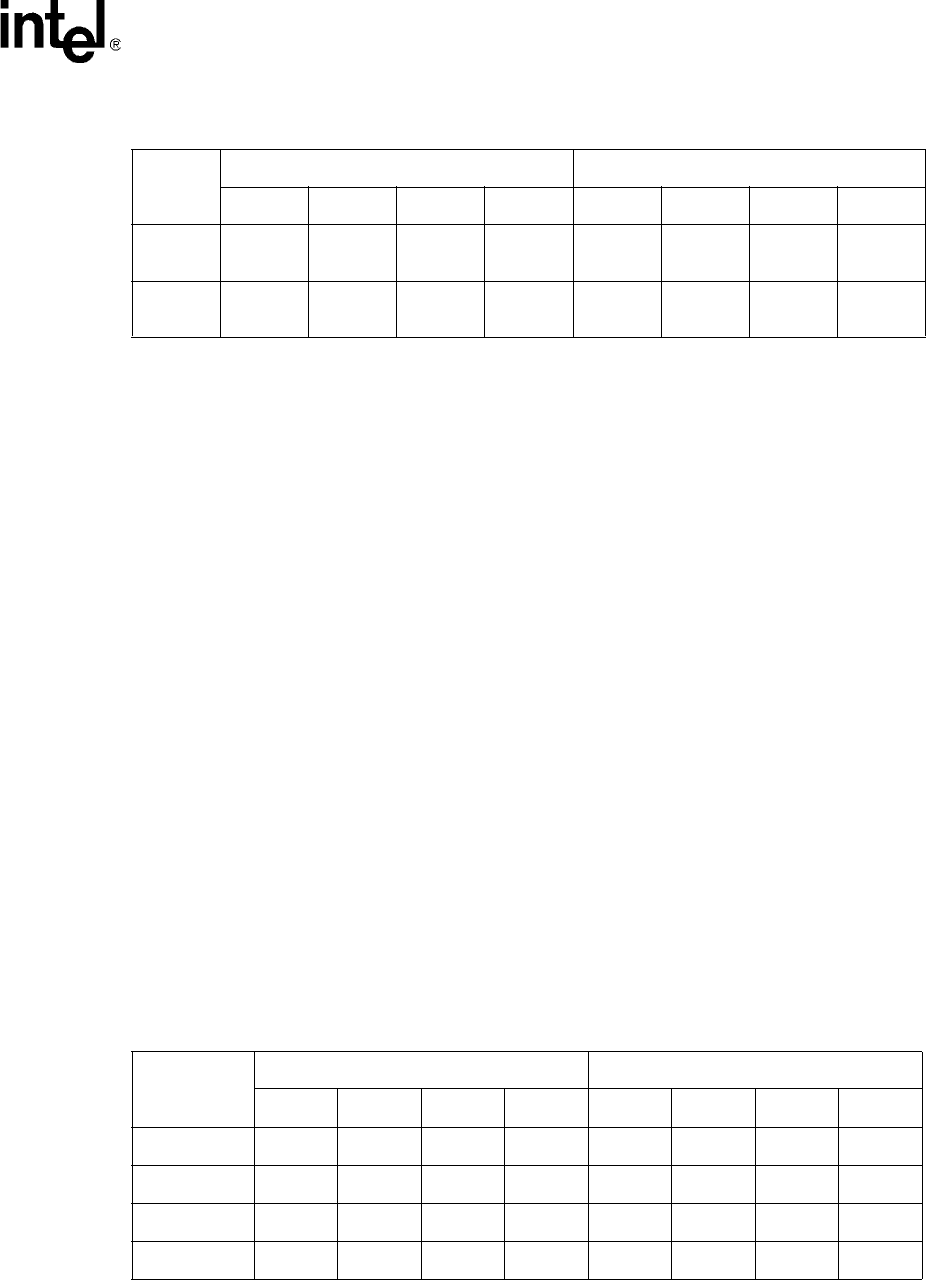

Table 46. Byte-Enable Generation by the Intel XScale

®

Core for 16-Bit Data Transfers in Little-

and Big-Endian Systems

Word to

be Read

Byte-Enables for Little-Endian System Byte-Enables for Big-Endian System

X_BE[0] X_BE[1] X_BE[2] X_BE[3] X_BE[0] X_BE[1] X_BE[2] X_BE[3]

Byte 0,

Byte 1

11000011

Byte 2,

Byte 3

00111100

Table 47. Byte-Enable Generation by the Intel XScale

®

Core for Byte Writes in Little- and

Big-Endian Systems

Byte Number

to be Written

Byte-Enables for Little-Endian Systems Byte-Enables for Big-Endian Systems

X_BE[0] X_BE[1] X_BE[2] X_BE[3] X_BE[0] X_BE[1] X_BE[2] X_BE[3]

Byte 0 10000001

Byte 1 01000010

Byte 2 00100100

Byte 3 00011000