Hardware Reference Manual 131

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.11.7 Gasket Local CSR

There are two sets of Control and Status registers residing in the gasket Local CSR space. ICSR

refers to the Interrupt CSR. The ICSR address range is 0xd600_0000 – 0xd6ff_ffff. The Gasket

CSR (GCSR) refers to the Hash CSRs and debug CSR. It has a range of

0xd700_0000 – 0xd7ff_ffff. GCSR is shown in Table 51.

Note: The Gasket registers are defined in the IXP2400 and IXP2800 Network Processor Programmer’s

Reference Manual.

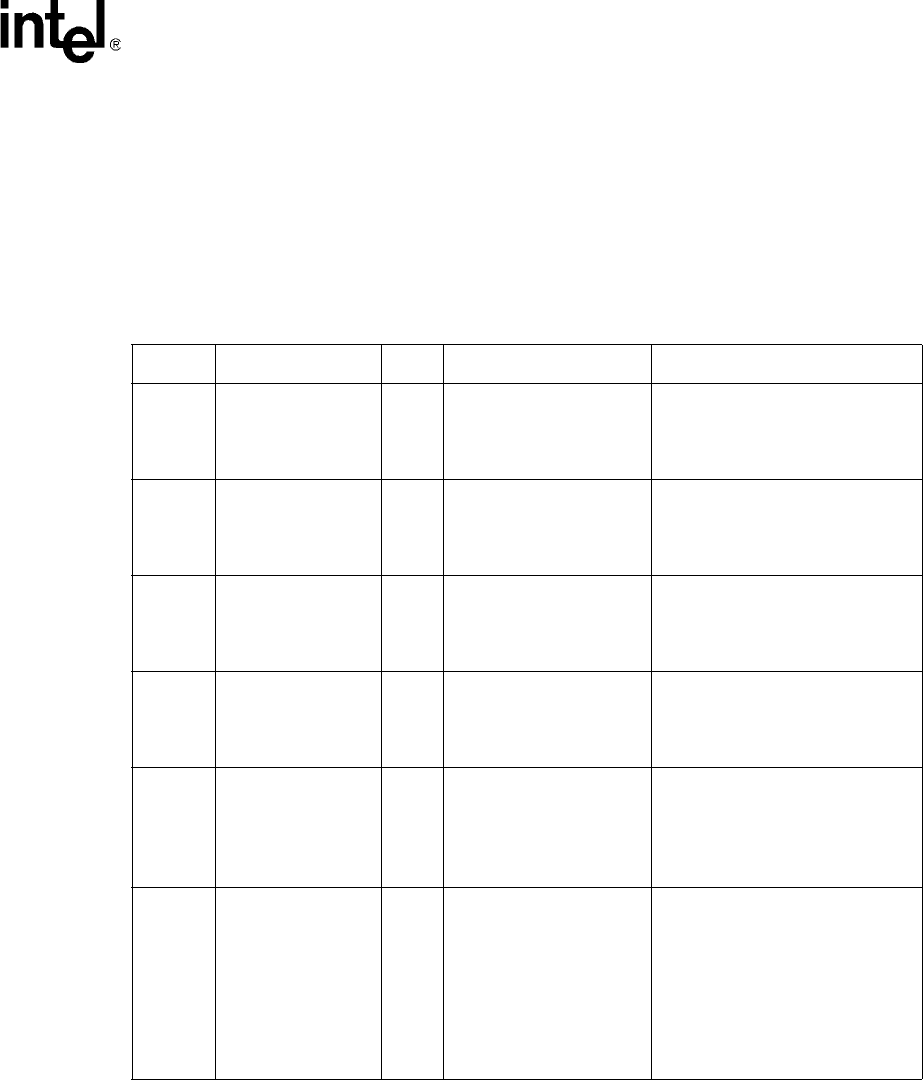

Table 51. GCSR Address Map (0xd700 0000)

Bits Name R/W Description Address Offset

[31:0] XG_GCSR_HASH0 R/W

Hash word 0

Write from Intel XScale

®

core.

Rd/Wr from CPP.

0x00—for 48-bit Hash

0x10—for 64-bit Hash

0x20—for 128-bit Hash

[31:0] XG_GCSR_HASH1 R/W

Hash word 1

Write from Intel XScale

®

core.

Rd/Wr from CPP.

0x04—for 48-bit Hash

0x14—for 64-bit Hash

0x24—for 128-bit Hash

[31:0] XG_GCSR_HASH2 R/W

Hash word 2

Write from Intel XScale

®

core.

Rd/Wr from CPP.

0x28—for 128-bit Hash

[31:0] XG_GCSR_HASH3 R/W

Hash word 3

Write from Intel XScale

®

core.

Rd/Wr from CPP.

0x2c—for 128-bit Hash

[31:0] XG_GCSR_CTR0 R

[31:1] reserved.

[0] hash valid flag.

Read from Intel XScale

®

core.

Set by LCSR control.

0x30

[31:0] XG_GCSR_CTR1 R/W

[31:1] reserved.

[0] Break_Function

When set to 1, the debug

break signal is used to stop

the clocks.

When set to 0, the debug

break signal is used to

cause an Intel XScale

®

core debug breakpoint

0x3c