156 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

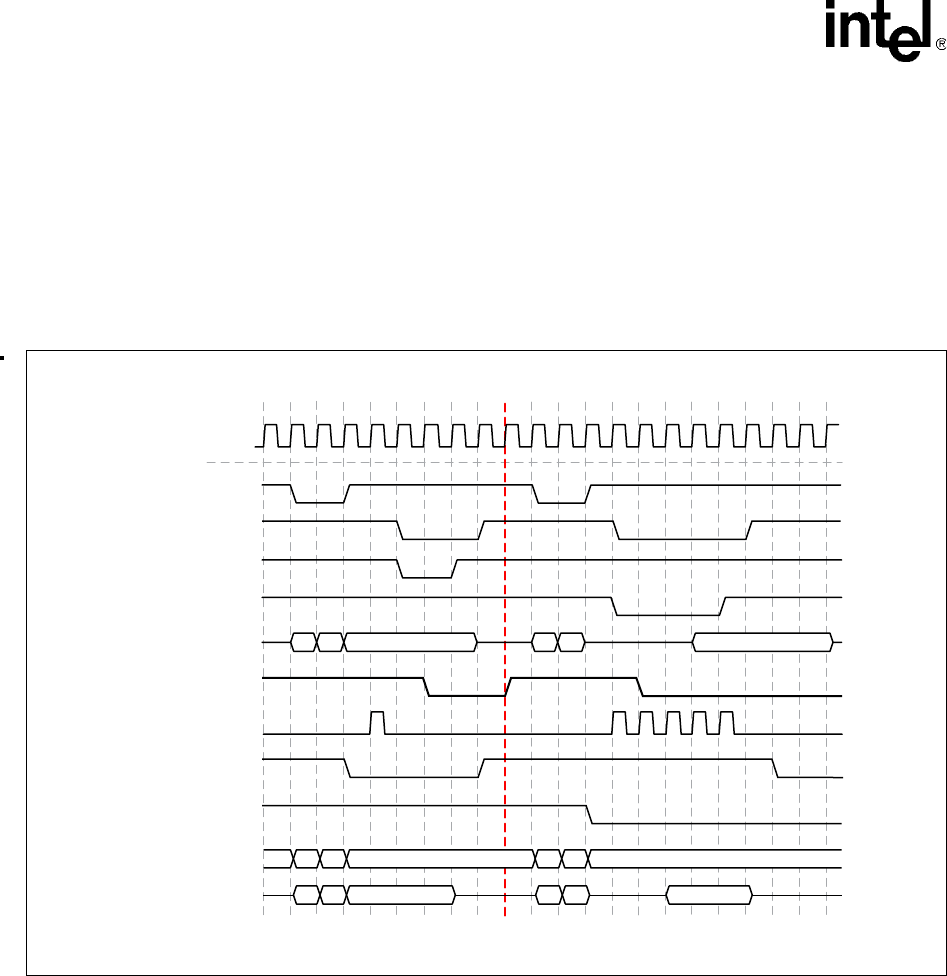

PMC-Sierra* PM5351 S/UNI-TETRA* Write Interface Protocol

Figure 46 depicts a single write transaction launched from the IXP2800 to the PMC-Sierra*

PM5351 device followed by single read transaction.

The write transaction for the PMC-Sierra* component has six clock cycles or a 120-ns access time

for a 50-MHz Slowport clock. In this case, no intervening cycle is added after the transaction. The

I/O throughput is 8.3 Mbytes per second. The SP_PCR should be programmed to mode 2 and the

fields of SU, PW, and HD in the SP_WTC2 should be set to 1, 2, and 1, respectively. Here, SU,

PW, and HD represent the SP_CS_L[1] pulse width, the SP_WR_L pulse width, and the SP_CP

pulse width, respectively.

PMC-Sierra* PM5351 S/UNI-TETRA* Read Interface Protocol

Figure 46. Mode 2 Single Write Transfer for PMC-Sierra* PM5351 Device (B0)

B1747-04

SP_CLK

SP_ALE_L

SP_CS_L[1]/CSB

SP_WR_L/WRB

SP_RD_L/RDB

20 4 6 8 10 12 14 16 18 20

SP_AD[7:0]

SP_ACK_L/INTB

SP_CP

SP_OE_L

A[10:0] A[10:0]

SP_DIR

ADDR[15:0]

DATA[7:0]

A

[10:8]

A

[10:8]

A

[7:0]

D[7:0]

A

[10:8]

A

[7:0]

D[7:0]

A

[15:8]

A

[7:0]

D[7:0] D[7:0]

A

[10:8]

A

[10:8]

A

[7:0]

A

[7:0]