238 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

SHaC — Unit Expansion

The Intel XScale

®

core initiates a hash operation by writing a set of memory-mapped Hash

Operand registers (which are built into the Intel XScale

®

core gasket) with the data to be used to

generate the hash index. There are separate registers for 48-, 64-, and 128-bit hashes. Only one

hash operation of each type can be done at a time. Writing to the last register in each group informs

the gasket logic that it has all of the operands for that operation, and it will then arbitrate for the

Command bus to send the command to the Hash Unit.

Note: Detailed information about CSRs is contained in the Intel

®

IXP2400 and IXP2800 Network

Processor Programmer’s Reference Manual.

For Microengine-generated commands and those generated by the Intel XScale

®

core, the

command enters the Command Inlet FIFO. As with the Scratchpad write and RMW operations,

signals are generated and sent to the Pull Arbiter. The Hash unit Pull Data FIFO allows the data for

up to three hash operations to be read into the Hash Unit in a single burst. When the command is

serviced, the first data to be hashed enters the hash array while the next two wait in the FIFO.

The Hash Unit uses a hard-wired polynomial algorithm and a programmable hash multiplier to

create hash indexes. Three separate multipliers are supported — one each, for 48-, 64-, and 128-bit

hash operations. The multiplier is programmed through the registers, HASH_MULTIPLIER_64_1,

HASH_MULTIPLIER_64_2, HASH_MULTIPLIER_48_1, HASH_MULTIPLIER_48_2,

HASH_MULTIPLIER_128_1, HASH_MULTIPLIER_128_2, HASH_MULTIPLIER_128_3, and

HASH_MULTIPLIER_128_4.

The multiplicand is shifted into the hash array 16 bits at a time. The hash array performs a

1’s-complement multiply and polynomial divide, calculated by using the multiplier and 16 bits of

the multiplicand. The result is placed into an output register and is also fed back into the array. This

process is repeated three times for a 48-bit hash (16 bits x 3 = 48), four times for a 64-bit hash

(16 bits x 4 = 64), and eight times for a 128-bit hash (16 x 8 = 128). After an entire multiplicand has

been passed through the hash array, the resulting hash index is placed into a two-stage output

pipeline and the next hash is immediately started.

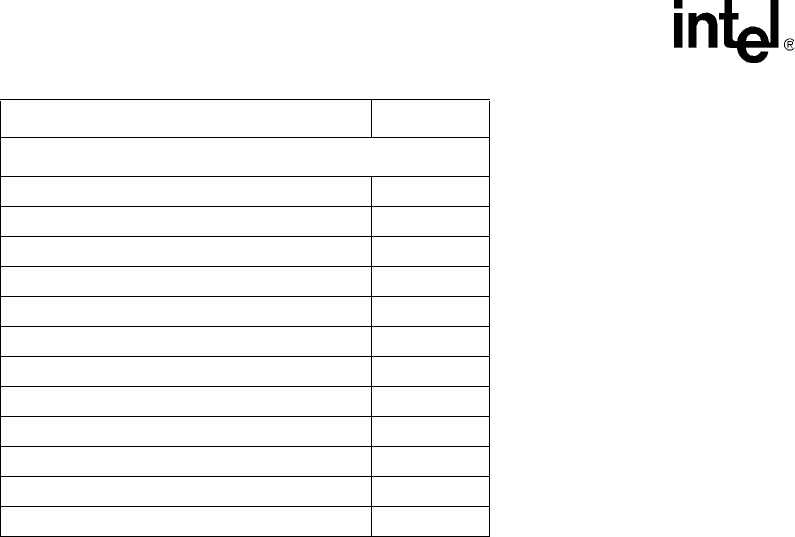

128-Bit Hash Operations

hash 3 [127:96] $xfer n+11

hash 3 [95:64] $xfer n+10

hash 3 [63:32] $xfer n+9

hash 3 [31:0] $xfer n+8

hash 2 [127:96] $xfer n+7

hash 2 [95:64] $xfer n+6

hash 2 [63:32] $xfer n+5

hash 2 [31:0] $xfer n+4

hash 1 [127:96] $xfer n+3

hash 1 [64:95] $xfer n+2

hash 1 [63:32] $xfer n+1

hash 1 [31:0] $xfer n

Table 82. S_Transfer Registers Hash Operands (Sheet 2 of 2)

Register Address