Hardware Reference Manual 205

Intel

®

IXP2800 Network Processor

DRAM

When a requestor gets a pull command on the CMD_BUS, the requestor sends the command to the

pull arbiter. This is enqueued into a requestor-dedicated FIFO. The pull request FIFOs are much

smaller than the push request FIFOs because pull requests can request up to 128 bytes of data. It is

eight entries deep and asserts full when it has six entries to account for in-flight requests.

The pull arbiter monitors the heads of each of the three FIFOs. A round robin arbitration scheme is

applied to all valid requests. When a request is granted, the request is completed regardless of how

many data transfers are required. Therefore, one request can take as many as 16 – 32 DRAM

cycles. The push data bus can only use 32 bits when delivering data to the Microengines, PCI, and

the Intel XScale

®

core. For these data sources, it takes two cycles to pull every eight bytes

requested; otherwise, it takes only one cycle per eight bytes. On four byte cycles, data is delivered

as pulled.

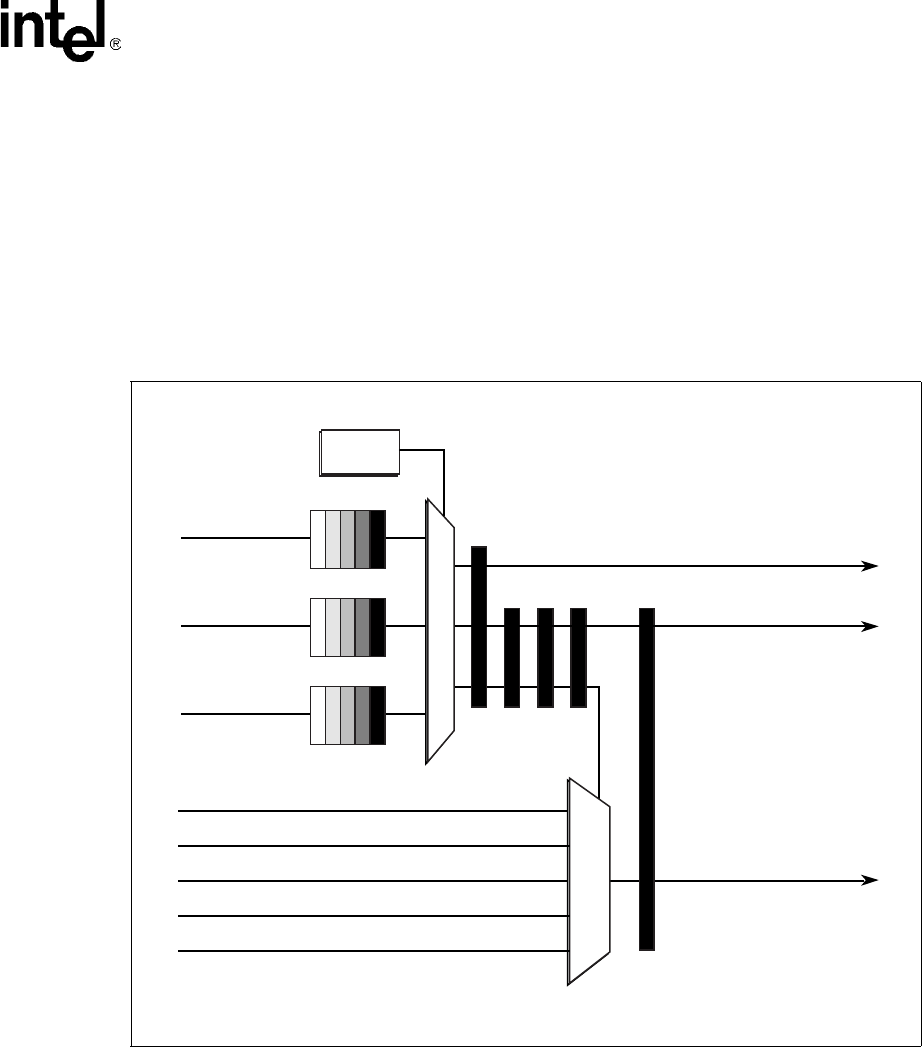

Figure 73. DRAM Pull Arbiter Functional Blocks

A9733-02

D0_PUSH_REQ

DPXX_PUSH_ID

Round

Robin

A

R

B

I

T

E

R

ME_CLUSTER_0_DATA

D0_PULL_ID

D1_PULL_ID

D2_PULL_ID

D1_PUSH_REQ

D2_PUSH_REQ

ME_CLUSTER_1_DATA

XSCALE*_DATA

* Intel XScale

®

Microarchitecture

PCI_PULL_DATA

MSF_PULL_DATA

DPXX_PULL_DATA[63:0]

DPXX_TAKE