292 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.8.5 From DRAM to TBUF for Instruction:

dram[tbuf_wr, --, src_op1, src_op2, ref_cnt], indirect_ref

For the transfers from DRAM, the TBUF acts like a slave. The address of the data to be written is

given in D_PUSH_ID. The data is registered and assembled from D_PUSH_BUS, and then written

into TBUF.

8.9 Receiver and Transmitter Interoperation with Framers and

Switch Fabrics

The Intel

®

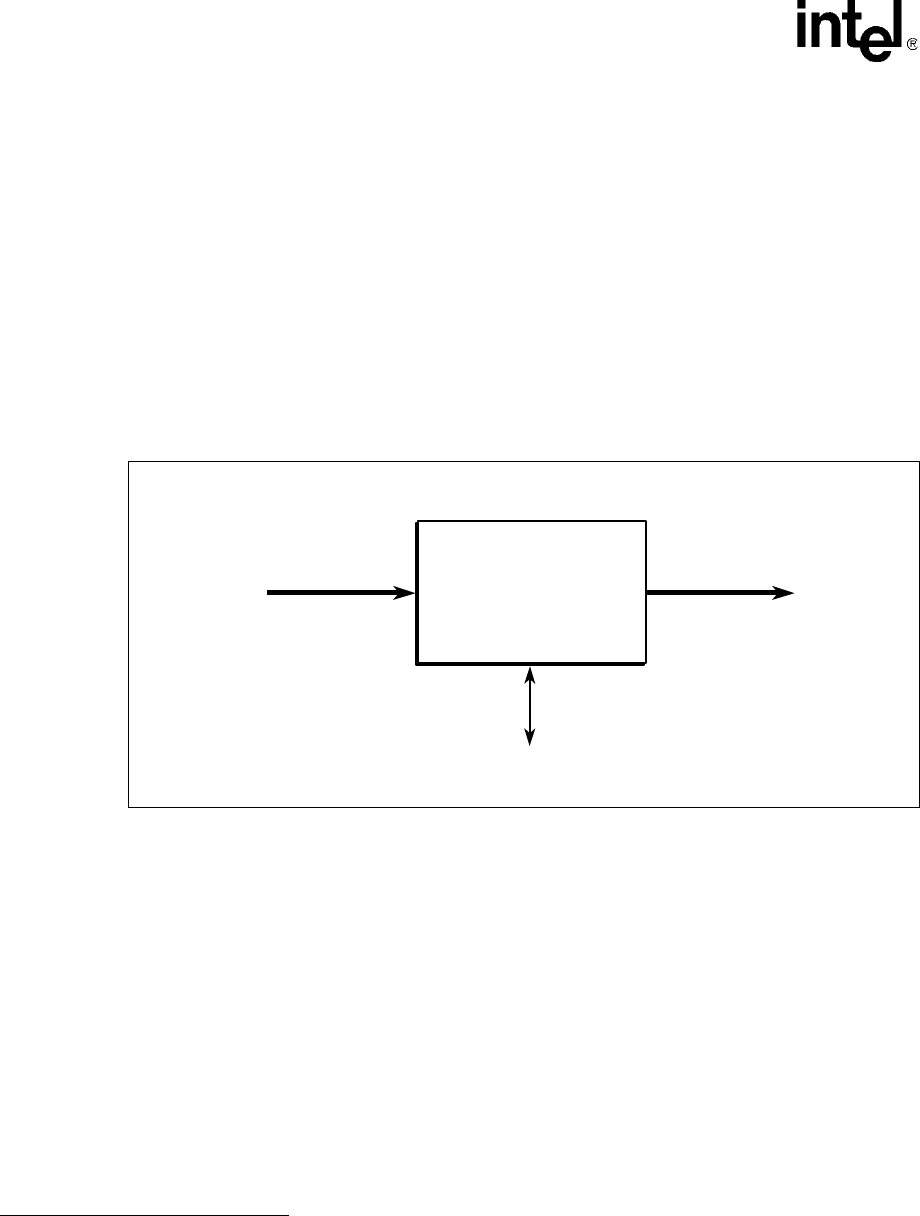

IXP2800 Network Processor can process data received at a peak rate of 16 Gb/s and

transmit data at a peak rate of 16 Gb/s. In addition, data may be received and transmitted via the

PCI bus at an aggregate peak rate of 4.2 Gb/s, as shown in Figure 101.

The network processor’s receiver and transmitter can be independently configured to support either

an SPI-4.2 framer interface or a fabric interface consisting of DDR LVDS signaling and the CSIX-

L1 protocol. The dynamic training sequence of SPI-4.2, used for de-skewing the signals, has been

optionally incorporated into the fabric interface.

“SPI-4.2 is an interface for packet and cell transfer between a physical layer (PHY) device and a

link layer device, for aggregate bandwidths of OC-192 ATM and Packet over SONET/SDH (POS),

as well as 10 Gb/s Ethernet applications.”

1

“CSIX-L1 is the Common Switch Interface. It defines a physical interface for transferring

information between a traffic manager (Network Processor) and a switching fabric…”

2

The

network processor adopts the protocol of CSIX-L1, but uses a DDR LVDS physical interface rather

than an LVCMOS or HSTL physical interface.

Figure 101. Basic I/O Capability of the Intel

®

IXP2800 Network Processor

B2734-01

Intel

®

IXP2800

Network

Processor

PCI

4.2 Gb/s

Peak

Transmitter

Receiver

16 Gb/s Peak 16 Gb/s Peak

1. “System Packet Interface Level 4 (SPI-4) Phase 2: OC-192 System Interface for Physical and Link Layer Devices,” Implementation

Agreement: OIF-SPI4-02.0, Optical Internetworking Forum

2. “CSIX-L1: Common Switch Interface Specification-L1,” CSIX