Hardware Reference Manual 127

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.11.2 Intel XScale

®

Core Gasket Functional Description

3.11.2.1 Command Memory Bus to Command Push/Pull Conversion

The primary function of the Intel XScale

®

core gasket unit is to translate commands initiated from

the Intel XScale

®

core in the Intel XScale

®

core command bus format, into the IXP2800 internal

command format (Command Push/Pull format).

Table 49 shows how many CPP commands are generated by the gasket from each CMB command.

Write data is guaranteed to be 32-bit (longword) aligned. Table 49 shows only the Store command.

In the Load case, the gasket simply converts it to the CPP format. No command splitting is

required. A Load can only be a byte (8 bits), a word (16 bits), longword (32 bits), or eight

longwords (8x32).

3.11.3 CAM Operation

In the SRAM controller, access ordering is guaranteed only for a read coming after a write. The

gasket enforces order rules in the following two cases.

1. Write coming after a read.

2. Read-Modify-Write coming after read.

The address CAMing is on 8-word boundaries. The SRAM effective address is 28 bits. Deduct

five bits (two bits for the word address and three bits for eight words), and the tag width for the

CAM is 23 bits wide. The CAM only operates on SRAM accesses.

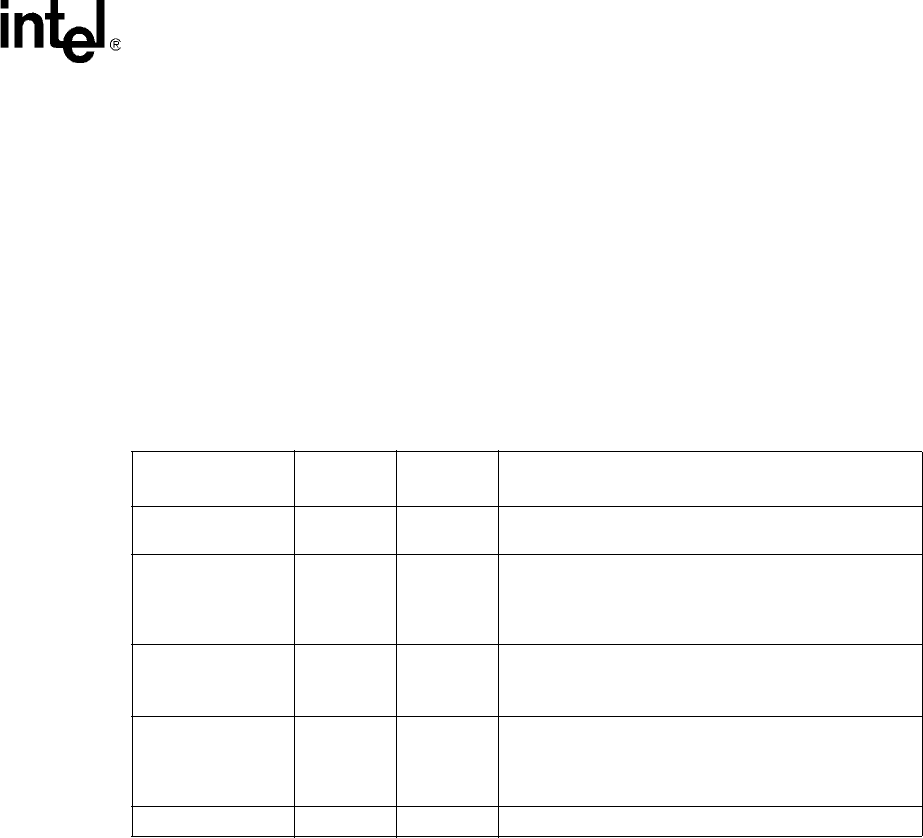

Table 49. CMB Write Command to CPP Command Conversion

Store Length

CPP SRAM

Cmd Count

CPP DRAM

Cmd Count

Remark

Byte, word,

longword

1 1 SRAM uses 4-bit mask, and DRAM uses an 8-bit mask.

2 longwords 1 or 2 1 or 2

SRAM: If there is any mask bit detected as ‘0’,two

commands will be generated.

DRAM: If it starts with odd word address, two commands

will be generated.

3 longwords 1 or 3 2

SRAM: If there is a mask bit of ‘0’ detected, Three SRAM

commands will be generated.

DRAM: always two DRAM commands.

4 longwords 1 or 4 1 or 2

SRAM: If there is a mask bit of ‘0’ detected, four

commands will be generated.

DRAM: If there is a mask bit of ‘0’ detected, two

commands will be generated.

8 longwords Not allowed in a write.