Hardware Reference Manual 361

Intel

®

IXP2800 Network Processor

Clocks and Reset

The fast frequency on the IXP2800 Network Processor is generated by an on-chip PLL that

multiplies a reference frequency provided by an on-board LVDS oscillator (frequency 100 MHz)

by a selectable multiplier. The multiplier is selected by using external strap pins SP_AD[5:0] and

can be viewed by software via the STRAP_OPTIONS[CFG_PLL_MULT] CAP CSR register bits.

The multiplier range is even multiples between 16 and 48, so the PLL can generate a 1.6 GHz to

4.8 GHz clock (with a 100-Mhz reference frequency).

The PLL output frequency is divided by 2 to get the Microengine clock and by 4 to get the Intel

XScale

®

core and the internal Command/Push/Pull bus frequency. An additional division (after the

divide by 2) is used to generate the clock frequencies for the other internal units. The divisors are

programmable via the CLOCK_CONTROL CSR. APB divisor specified in the

CLOCK_CONTROL CSR clock is scaled by 4 (i.e., a value of 2 in the CSR selects a divisor of 8).

Table 148 shows the frequencies that are available based on a 100-Mhz oscillator and various

values of PLL multipliers, for the supported divisor values of 3 to 15.

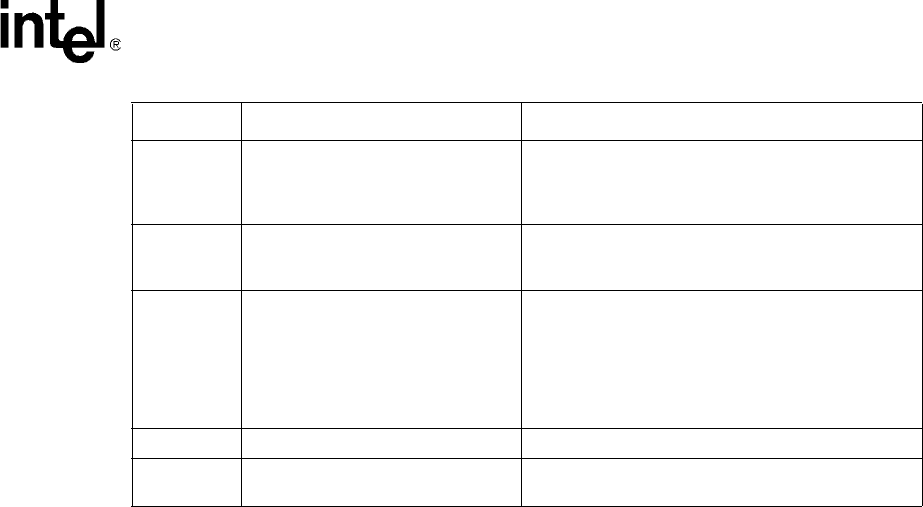

SRAM

SRAM pins and control logic (all of

the SRAM unit except Internal Bus

interface).

Divide of Microengine frequency. Each SRAM channel

has its own frequency selection. Clocks are driven by

the IXP2800 Network Processor to external SRAMs

and/or Coprocessors.

Scratch,

Hash, CSR

Scratch RAM, Hash Unit, CSR

access block

1/2 of Microengine frequency. Note that Slowport has

no clock. Timing for Slowport accesses is defined in

Slowport registers.

MSF

Receive and Transmit pins and

control logic.

The transmit clock for the Media and Switch interface

can be derived in two different ways.

• From TCLK input signal (supplied by PHY device).

• Divided from internal clock.

For details please refer to Chapter 8, “Media and

Switch Fabric Interface”.

APB APB logic Divide of Microengine frequency.

PCI PCI pins and control logic.

External reference. Either from Host system or on-

board oscillator.

Table 147. Clock Usage Summary (Sheet 2 of 2)

Unit Name Description Comment