Hardware Reference Manual 41

Intel

®

IXP2800 Network Processor

Technical Description

In Example 8, the second instruction will access the Local Memory location one past the source/

destination of the first.

2.3.5 Addressing Modes

GPRs can be accessed in either a context-relative or an absolute addressing mode. Some

instructions can specify either mode; other instructions can specify only Context-Relative mode.

Transfer and Next Neighbor registers can be accessed in Context-Relative and Indexed modes, and

Local Memory is accessed in Indexed mode. The addressing mode in use is encoded directly into

each instruction, for each source and destination specifier.

2.3.5.1 Context-Relative Addressing Mode

The GPRs are logically subdivided into equal regions such that each Context has relative access to

one of the regions. The number of regions is configured in the CTX_ENABLE CSR, and can be

either 4 or 8. Thus a Context-Relative register number is actually associated with multiple different

physical registers. The actual register to be accessed is determined by the Context making the

access request (the Context number is concatenated with the register number specified in the

instruction). Context-Relative addressing is a powerful feature that enables eight (or four) different

contexts to share the same code image, yet maintain separate data.

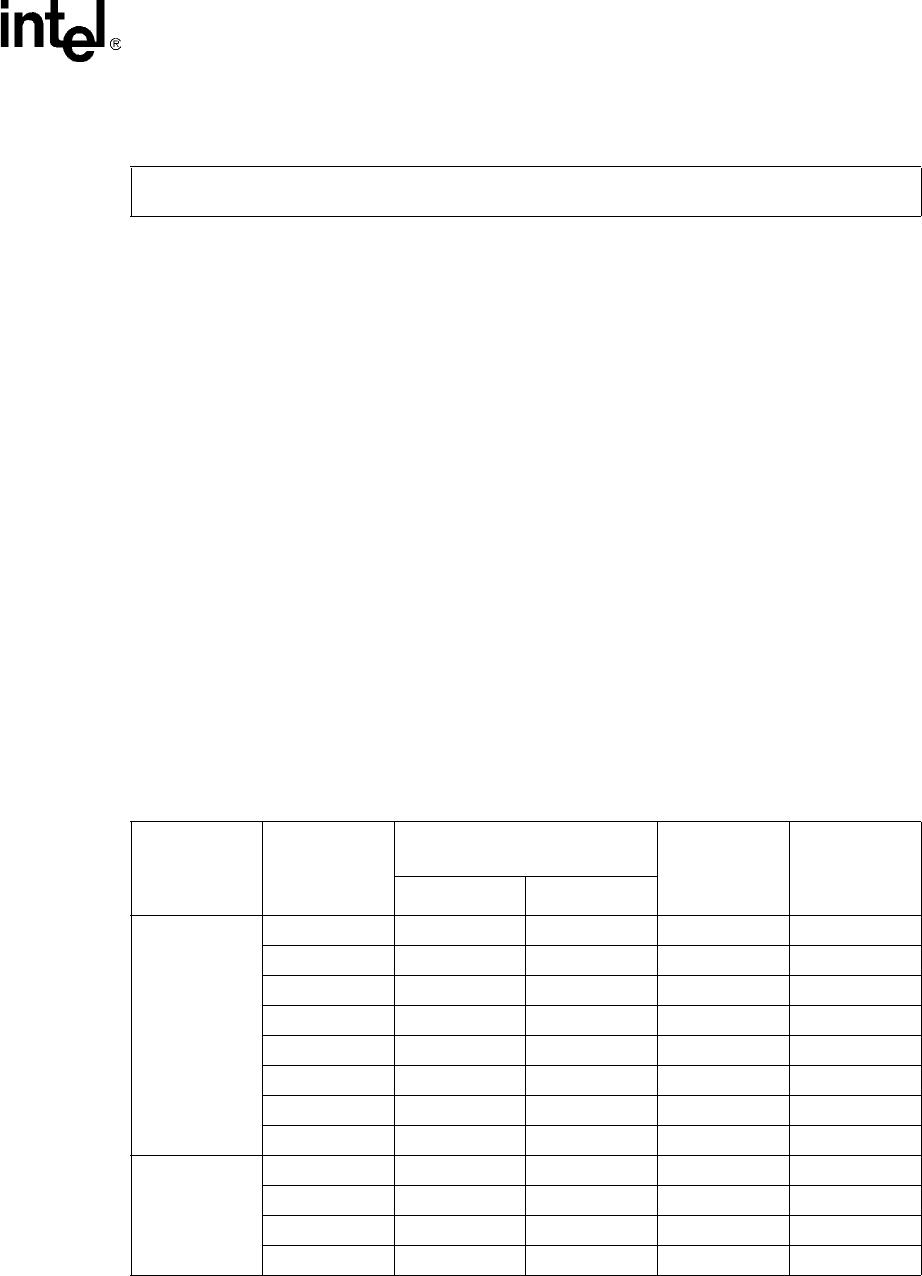

Table 5 shows how the Context number is used in selecting the register number in relative mode.

The register number in Table 5 is the Absolute GPR address, or Transfer or Next Neighbor Index

number to use to access the specific Context-Relative register. For example, with eight active

Contexts, Context-Relative Register 0 for Context 2 is Absolute Register Number 32.

Example 8. LM_ADDR Post-Increment

alu[*l$index0++, --, ~B, gpr_n]

alu[gpr_m, --, ~B, *l$index0]

Table 5. Registers Used By Contexts in Context-Relative Addressing Mode

Number of

Active

Contexts

Active

Context

Number

GPR

Absolute Register Numbers

S_Transfer or

Neighbor

Index Number

D_Transfer

Index Number

A Port B Port

8

(Instruction

always specifies

registers in

range 0 – 15)

0 0 – 15 0 – 15 0 – 15 0 – 15

1 16 – 31 16 – 31 16 – 31 16 – 31

2 32 – 47 32 – 47 32 – 47 32 – 47

3 48 – 63 48 – 63 48 – 63 48 – 63

4 64 – 79 64 – 79 64 – 79 64 – 79

5 80 – 95 80 – 95 80 – 95 80 – 95

6 96 – 111 96 – 111 96 – 111 96 – 111

7 112 – 127 112 – 127 112 – 127 112 – 127

4

(Instruction

always specifies

registers in

range 0 – 31)

0 0 – 31 0 – 31 0 – 31 0 – 31

2 32 – 63 32 – 63 32 – 63 32 – 63

4 64 – 95 64 – 95 64 – 95 64 – 95

6 96 – 127 96 – 127 96 – 127 96 – 127