84 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

If the Line Allocation Policy is read-allocate, all load operations that miss the cache request a

32-byte cache line from external memory and allocate it into either the data cache or mini-data

cache (this is assuming the cache is enabled). Store operations that miss the cache will not cause a

line to be allocated.

If read/write-allocate is in effect, load or store operations that miss the cache will request a 32-byte

cache line from external memory if the cache is enabled.

The other policy determined by the X, C, and B bits is the Write Policy. A write-through policy

instructs the Data Cache to keep external memory coherent by performing stores to both external

memory and the cache. A write-back policy only updates external memory when a line in the cache

is cleaned or needs to be replaced with a new line. Generally, write-back provides higher

performance because it generates less data traffic to external memory.

3.3.1.2.5 Memory Operation Ordering

A fence memory operation (memop) is one that guarantees all memops issued prior to the fence

will execute before any memop issued after the fence. Thus software may issue a fence to impose a

partial ordering on memory accesses.

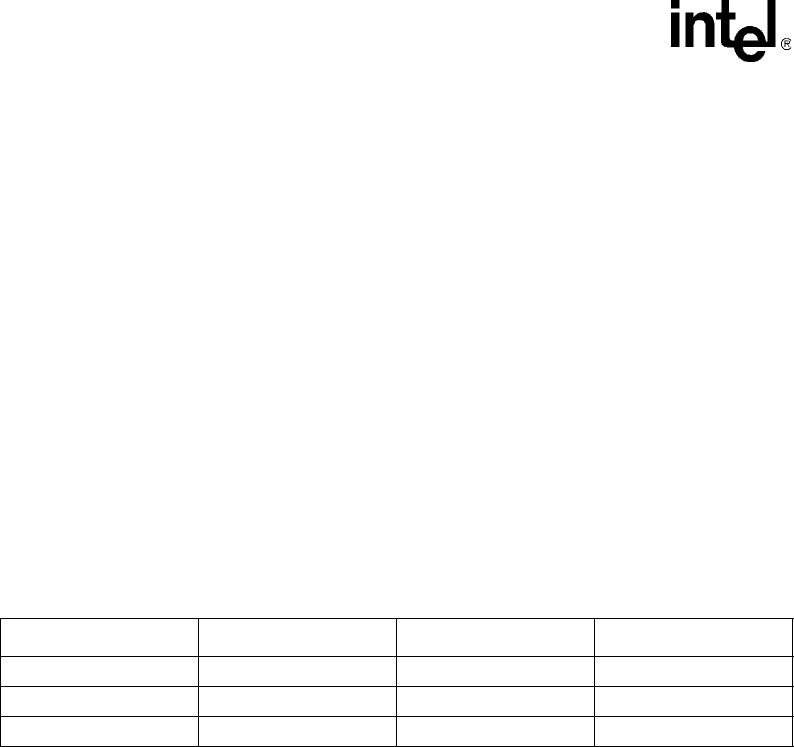

Table 22 shows the circumstances in which memops act as fences.

Any swap (SWP or SWPB) to a page that would create a fence on a load or store is a fence.

3.3.2 Exceptions

The MMU may generate prefetch aborts for instruction accesses and data aborts for data memory

accesses.

Data address alignment checking is enabled by setting bit 1 of the Control register (CP15,

register 1). Alignment faults are still reported even if the MMU is disabled. All other MMU

exceptions are disabled when the MMU is disabled.

Table 22. Memory Operations that Impose a Fence

operation X C B

load — 0 —

store101

load or store 0 0 0