User’s Manual

PPC440x5 CPU Core Preliminary

Page 110 of 589

cache.fm.

September 12, 2002

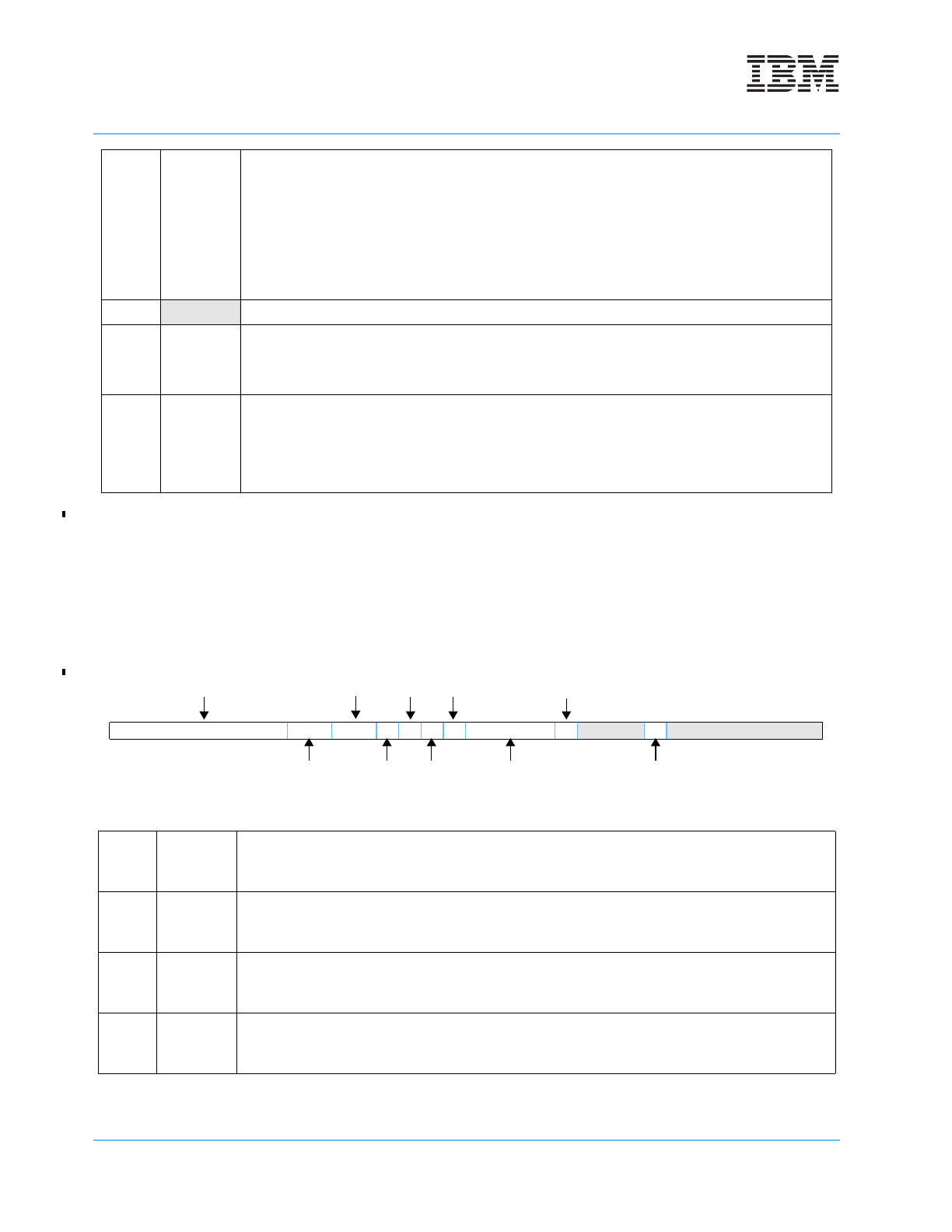

4.2.4.3 Core Configuration Register 1 (CCR1)

The CCR1 register controls parity error insertion for software testing, one option for line flush behavior in the

D-cache, and a control bit that selects the timer input clock. Each of the these functions is discussed in more

detail in the related sections of this manual.

Figure 4-6 illustrates the fields of the CCR1 register.

23 FLSTA

Force Load/Store Alignment

0 No Alignment exception on integer

storage access instructions, regardless

of alignment

1 An alignment exception occurs on

integer storage access instructions if

data address is not on an operand

boundary.

See Load and Store Alignment on page 117.

24:27

Reserved

28:29 ICSLC Instruction Cache Speculative Line Count

Number of additional lines (0–3) to fill on instruc-

tion fetch miss.

See Speculative Prefetch Mechanism on

page 105.

30:31 ICSLT Instruction Cache Speculative Line Threshold

Number of doublewords that must have already

been filled in order that the current speculative

line fill is not abandoned on a redirection of the

instruction stream.

See Speculative Prefetch Mechanism on

page 105.

Figure 4-6. Core Configuration Register 1 (CCR1)

0:7 ICDPEI

Instruction Cache Data Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded when the

instruction cache is filled. Each of the 8 bits corre-

sponds to one of the instruction words in the line.

8:9 ICTPEI

Instruction Cache Tag Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the instruction cache.

10:11 DCTPEI

Data Cache Tag Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the data cache.

12 DCDPEI

Data Cache Data Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded for the

data field in the data cache.

0 7 8 9 10 11 12 13 14 15 16 19 20 21 23 24 25 31

MMUPEIDCMPEI

DCUPEI

FCOM

FFF

TCS

DCTPEI

DCDPEI

ICDPEI

ICTPEI