User’s Manual

Preliminary PPC440x5 CPU Core

prgmodel.fm.

September 12, 2002

Page 73 of 589

2.6.2.1 Summary Overflow (SO) Field

This field is set to 1 when an instruction is executed that causes XER[OV] to be set to 1, except for the case

of mtspr(XER), which writes XER[SO,OV] with the values in (RS)

0:1

, respectively. Once set, XER[SO] is not

reset until either an mtspr(XER) is executed with data that explicitly writes 0 to XER[SO], or until an mcrxr

instruction is executed. The mcrxr instruction sets XER[SO] (as well as XER[OV,CA]) to 0 after copying all

three fields into CR[CR0]

0:2

(and setting CR[CR0]

3

to 0).

Given this behavior, XER[SO] does not necessarily indicate that an overflow occurred on the most recent

integer arithmetic operation, but rather that one occurred at some time subsequent to the last clearing of

XER[SO] by mtspr(XER) or mcrxr.

XER[SO] is read (along with the rest of the XER) into a GPR by mfspr(XER). In addition, various integer

instructions copy XER[SO] into CR[CR0]

3

(see Condition Register (CR) on page 67).

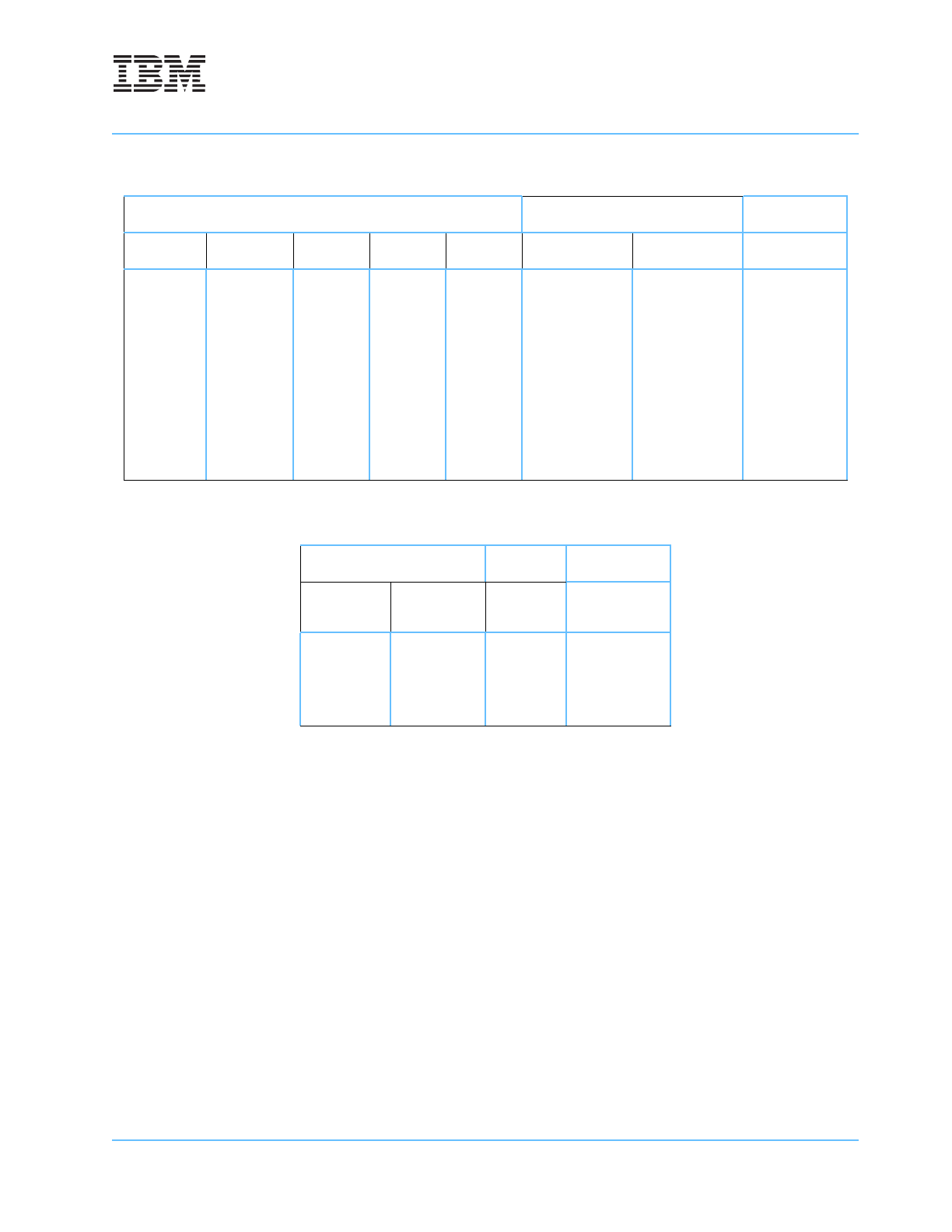

Table 2-25. XER[SO,OV] Updating Instructions

Integer Arithmetic Auxiliary Processor

Processor Con-

trol

Add Subtract Multiply Divide Negate

Multiply-Accumu-

late

Negative Multi-

ply- Accumulate

Register Man-

agement

addo[.]

addco[.]

addeo[.]

addmeo[.]

addzeo[.]

subfo[.]

subfco[.]

subfeo[.]

subfmeo[.]

subfzeo[.]

mullwo[.]

divwo[.]

divwuo[.]

nego[.]

macchwo[.]

macchwso[.]

macchwsuo[.]

macchwuo[.]

machhwo[.]

machhwso[.]

machhwsuo[.]

machhwuo[.]

maclhwo[.]

maclhwso[.]

maclhwsuo[.]

maclhwuo[.]

nmacchwo[.]

nmacchwso[.]

nmachhwo[.]

nmachhwso[.]

nmaclhwo[.]

nmaclhwso[.]

mtspr

mcrxr

Table 2-26. XER[CA] Updating Instructions

Integer Arithmetic

Integer

Shift

Processor

Control

Add Subtract

Shift

Right

Algebraic

Register

Management

addc[o][.]

adde[o][.]

addic[.]

addme[o][.]

addze[o][.]

subfc[o][.]

subfe[o][.]

subfic

subfme

[o][.]

subfze[o][.]

sraw[.]

srawi[.]

mtspr

mcrxr