DBCR0 (cont.)

Debug Control Register 0

PPC440x5 CPU Core User’s Manual Preliminary

Page 470 of 589

regsumm440core.fm.

September 12, 2002

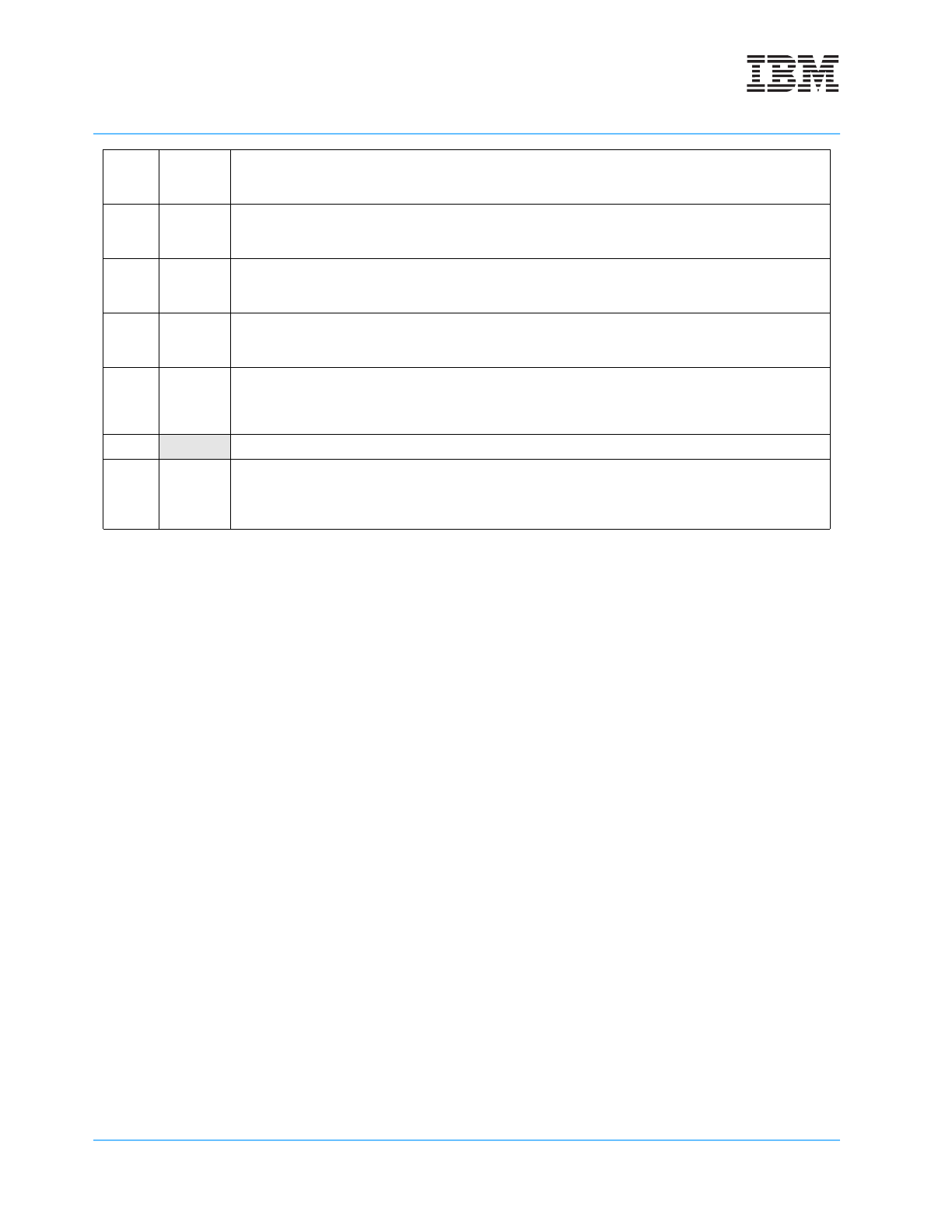

12 DAC1R

Data Address Compare (DAC) 1 Read Debug Event

0 Disable DAC 1 read debug event.

1 Enable DAC 1 read debug event.

13 DAC1W

DAC 1 Write Debug Event

0 Disable DAC 1 write debug event.

1 Enable DAC 1 write debug event.

14 DAC2R

DAC 2 Read Debug Event

0 Disable DAC 2 read debug event.

1 Enable DAC 2 read debug event.

15 DAC2W

DAC 2 Write Debug Event

0 Disable DAC 2 write debug event.

1 Enable DAC 2 write debug event.

16 RET

Return Debug Event

0 Disable return (rfi/rfci/rfmci) debug event.

1 Enable return (rfi/rfci/rfmci) debug event.

rfci/rfmci does not cause a return

debug event if MSR[DE] = 0 in internal

debug mode, unless also in external

debug mode or debug wait mode.

17:30 Reserved

31 FT

Freeze timers on debug event

0 Timers are not frozen.

1 Freeze timers if a DBSR field associated with a debug event

is set.