User’s Manual

PPC440x5 CPU Core Preliminary

Page 40 of 589

prgmodel.fm.

September 12, 2002

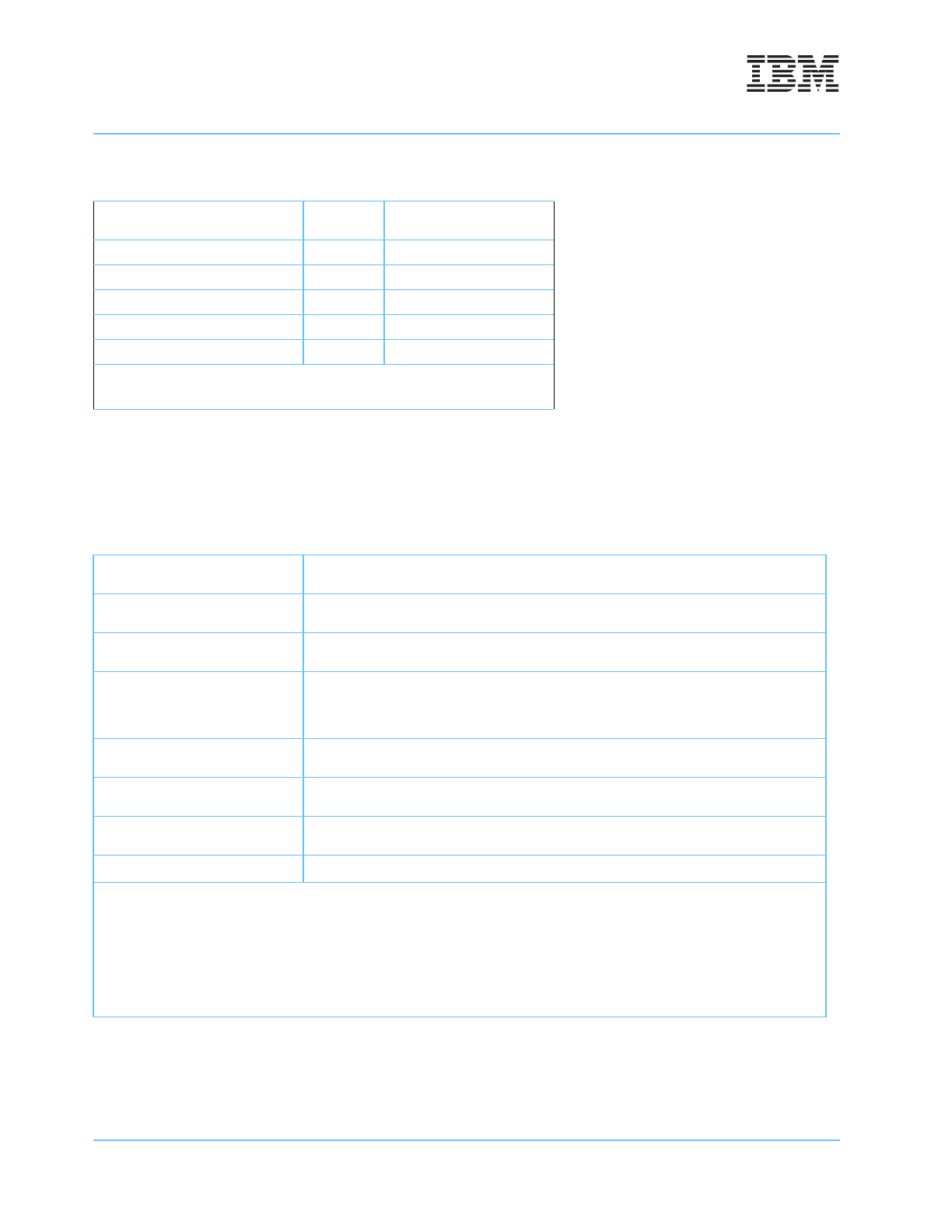

Data storage operands for storage access instructions have the following characteristics.

The alignment of the operand effective address of some storage access instructions may affect performance,

and in some cases may cause an Alignment exception to occur. For such storage access instructions, the

best performance is obtained when the storage operands are aligned. Table 2-2 summarizes the effects of

alignment on those storage access instruction types for which such effects exist. If an instruction type is not

shown in the table, then there are no alignment effects for that instruction type.

Cache management instructions access cache block operands, and for the PPC440x5 core the cache block

size is 32 bytes. However, the effective addresses calculated by cache management instructions are not

required to be aligned on cache block boundaries. Instead, the architecture specifies that the associated low-

order effective address bits (bits 27:31 for PPC440x5) are ignored during the execution of these instructions.

Table 2-1. Data Operand Definitions

Storage Access Instruction

Type

Operand

Length

Addr[28:31] if aligned

Byte (or String) 8 bits 0bxxxx

Halfword 2 bytes 0bxxx0

Word (or Multiple) 4 bytes 0bxx00

Doubleword (AP only) 8 bytes 0bx000

Quadword (AP only) 16 bytes 0b0000

Note: An “x” in an address bit position indicates that the bit can be 0

or 1 independent of the state of other bits in the address.

Table 2-2. Alignment Effects for Storage Access Instructions

Storage Access

InstructionType

Alignment Effects

Integer load/store halfword

Broken into two byte accesses if crosses 16-byte boundary (EA[28:31] = 0b1111); otherwise

no effect

Integer load/store word

Broken into two accesses if crosses 16-byte boundary (EA[28:31] > 0b1100); otherwise no

effect

Integer load/store multiple or string

Broken into a series of 4-byte accesses until the last byte is accessed or a 16-byte boundary is

reached, whichever occurs first. If bytes remain past a 16-byte boundary, resume accessing 4

bytes at a time until the last byte is accessed or the next 16-byte boundary is reached, which-

ever occurs first; repeat.

AP load/store halfword

Alignment exception if crosses 16-byte boundary (EA[28:31] = 0b1111); otherwise no effect

(see note)

AP load/store word

Alignment exception if crosses 16-byte boundary (EA[28:31] > 0b1100); otherwise no effect

(see note)

AP load/store doubleword

Alignment exception if crosses 16-byte boundary (EA[28:31] > 0b1000); otherwise no effect

(see note)

AP load/store quadword

Alignment exception if crosses 16-byte boundary (EA[28:31] ≠ 0b0000); otherwise no effect

Note: An auxiliary processor can specify that the EA for a given AP load/store instruction must be aligned at the

operand-size boundary, or alternatively, at a word boundary. If the AP so indicates this requirement and the

calculated EA fails to meet it, the PPC440x5 core generates an Alignment exception. Alternatively, an

auxiliary processor can specify that the EA for a given AP load/store instruction should be “forced” to be

aligned, by ignoring the appropriate number of low-order EA bits and processing the AP load/store as if

those bits were 0. Byte, halfword, word, doubleword, and quadword AP load/store instructions would ignore

0, 1, 2, 3, and 4 low-order EA bits, respectively.