CCR1

Core Configuration Register 1

PPC440x5 CPU Core User’s Manual Preliminary

Page 462 of 589

regsumm440core.fm.

September 12, 2002

CCR1

SPR 0x378 Supervisor R/W

See Core Configuration Register 1 (CCR1) on page 110.

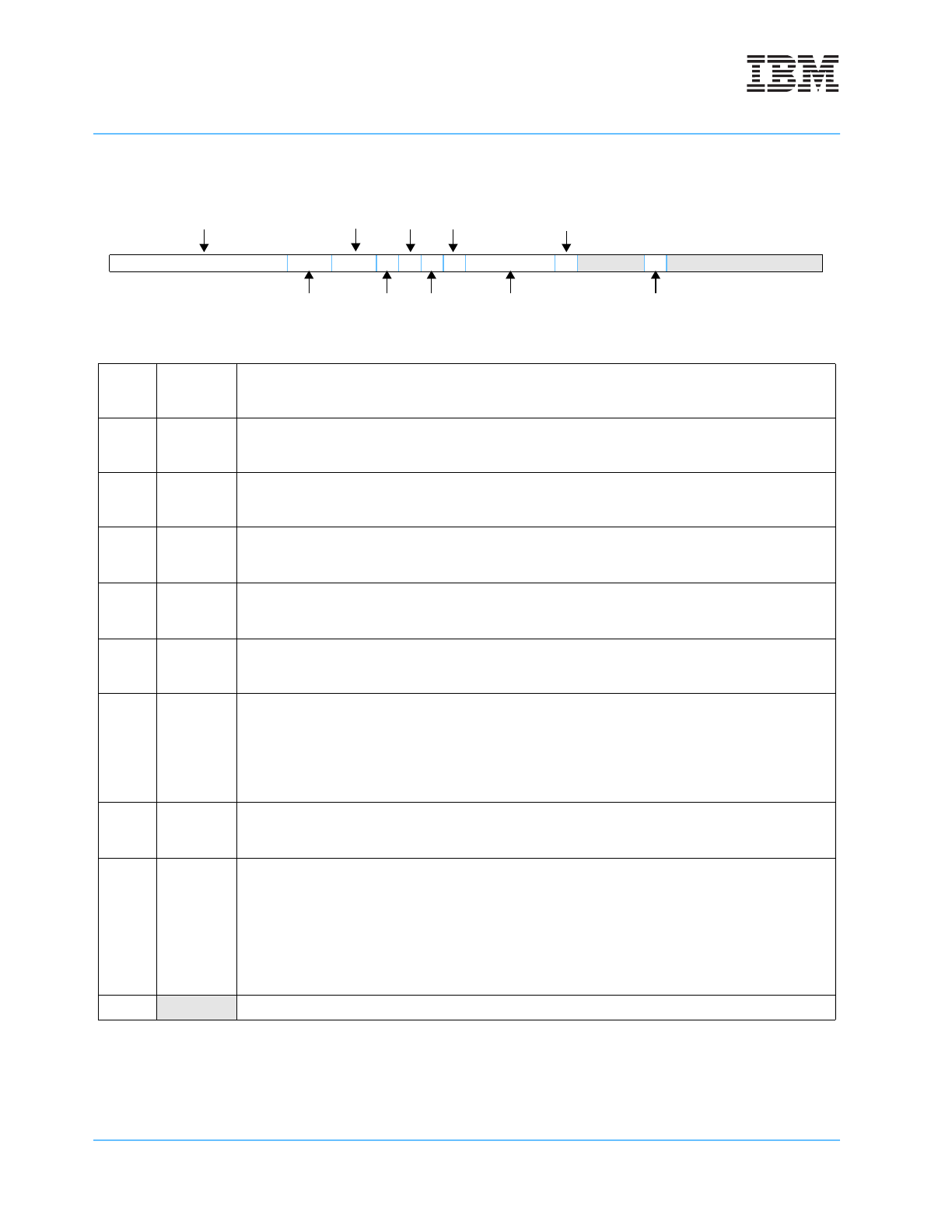

Figure 10-2. Core Configuration Register 1 (CCR1)

0:7 ICDPEI

Instruction Cache Data Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded when the

instruction cache is filled. Each of the 8 bits corre-

sponds to one of the instruction words in the line.

8:9 ICTPEI

Instruction Cache Tag Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the instruction cache.

10:11 DCTPEI

Data Cache Tag Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the data cache.

12 DCDPEI

Data Cache Data Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded for the

data field in the data cache.

13 DCUPEI

Data Cache U-bit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bit recorded for the U

fields in the data cache.

14 DCMPEI

Data Cache Modified-bit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded for the

modified (dirty) field in the data cache.

15 FCOM

Force Cache Operation Miss

0 normal operation

1 cache ops appear to miss the cache

Force icbt , dcbt, dcbtst, dcbst, dcbf, dcbi, and

dcbz to appear to miss the caches. The intended

use is with icbt and dcbt only, which will fill a dupli-

cate line and allow testing of multi-hit parity errors.

See Section 4.2.4.7 Simulating Instruction Cache

Parity Errors for Software Testing on page 114 and

Figure 4.3.3.7 on page 130.

16:19 MMUPEI

Memory Management Unit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the MMU.

20 FFF

Force Full-line Flush

0 flush only as much data as necessary.

1 always flush entire cache lines

When flushing 32-byte (8-word) lines from the data

cache, normal operation is to write nothing, a dou-

ble word, quad word, or the entire 8-word block to

the memory as required by the dirty bits. This bit

ensures that none or all dirty bits are set so that

either nothing or the entire 8-word block is written

to memory when flushing a line from the data

cache. Refer to Section 4.3.1.4 Line Flush Opera-

tions on page 121.

21:23

Reserved

0 7 8 9 10 11 12 13 14 15 16 19 20 21 23 24 25 31

MMUPEIDCMPEI

DCUPEI

FCOM

FFF

TCS

DCTPEI

DCDPEI

ICDPEI

ICTPEI