User’s Manual

PPC440x5 CPU Core Preliminary

Page 168 of 589

intrupts.fm.

September 12, 2002

6.4.4 Critical Save/Restore Register 0 (CSRR0)

CSRR0 is an SPR that is used to save machine state on critical interrupts, and to restore machine state when

an rfci is executed. When a critical interrupt occurs, CSRR0 is set to an address associated with the process

which was executing at the time. When rfci is executed, instruction execution returns to the address in

CSRR0.

In general, CSRR0 contains the address of the instruction that caused the critical interrupt, or the address of

the instruction to return to after a critical interrupt is serviced. See the individual descriptions under Interrupt

Definitions on page 175 for an explanation of the precise address recorded in CSRR0 for each critical inter-

rupt type.

CSRR0 can be written from a GPR using mtspr, and can be read into a GPR using mfspr.

6.4.5 Critical Save/Restore Register 1 (CSRR1)

CSRR1 is an SPR that is used to save machine state on critical interrupts, and to restore machine state when

an rfci is executed. When a critical interrupt is taken, the contents of the MSR (prior to the MSR being

cleared by the interrupt) are placed into CSRR1. When rfci is executed, the MSR is restored with the

contents of CSRR1.

Bits of CSRR1 that correspond to reserved bits in the MSR are also reserved.

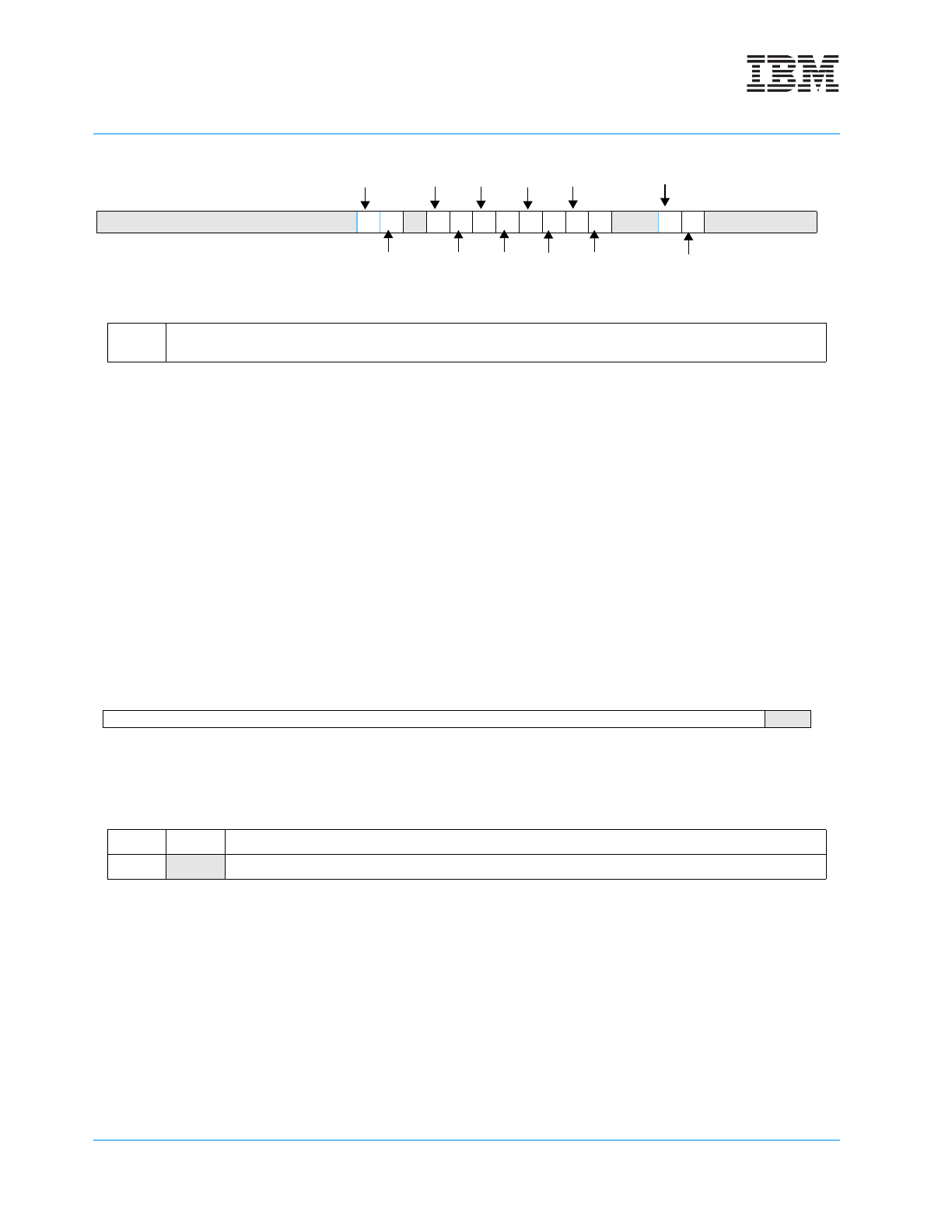

Figure 6-3. Save/Restore Register 1 (SRR1)

0:31

Copy of the MSR at the time of a non-critical inter-

rupt.

Figure 6-4. Critical Save/Restore Register 0 (CSRR0)

0:29 Return address for critical interrupts

30:31 Reserved

0 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 31

FE1

WE

PR

DS

CE

EE

DE

FP

ME

DWE

FE0

IS

0 29 30 31