User’s Manual

Preliminary PPC440x5 CPU Core

debug.fm.

September 12, 2002

Page 225 of 589

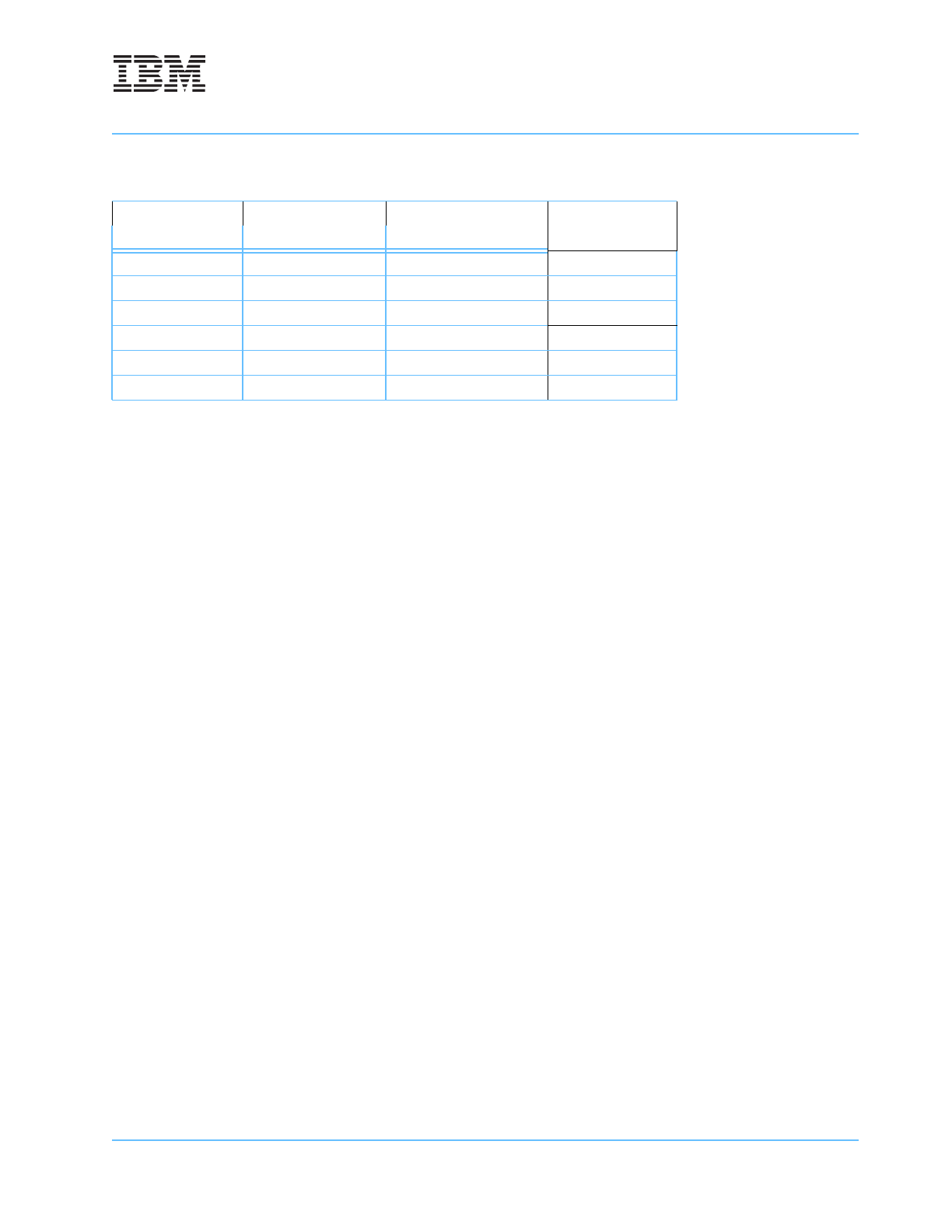

status fields is summarized in Table 8-2

The affect of the auto-toggle mechanism is to cause the IAC mode to switch back and forth

between range inclusive mode and range exclusive mode, as each IAC range mode debug event

occurs. For example, if the IAC mode is set to range inclusive, and auto-toggle is enabled, and

the auto-toggle status field is 0, then the first IAC debug event will be a range inclusive event.

Upon that event, the DBSR auto-toggle status field will be set to 1, and the next IAC debug event

will then be a range exclusive event. Upon this next event, the DBSR auto-toggle status field will

be set back to 0, such that the next IAC debug event will again be a range inclusive event.

This auto-toggling between range inclusive and range exclusive IAC modes is particularly helpful

when enabling IAC range mode debug events in trace debug mode. A common debug operation

is to detect when the instruction stream enters a particular region of the instruction address space

(range inclusive mode). Once having entered the region of interest (a range inclusive event), it is

common for the debugger to then want to be informed when that region is exited (a range

exclusive event). By automatically toggling to range exclusive mode upon the occurrence of the

range inclusive IAC debug event, this particular debug operation is facilitated. Furthermore, by

not remaining in range inclusive mode upon entry to the region of interest, the debugger avoids a

continuous stream of range inclusive IAC debug events while the processor continues to execute

instructions within that region, which can often be for a very long series of instructions.

8.3.1.2 IAC Debug Event Processing

When operating in external debug mode or debug wait mode, the occurrence of an IAC debug event is

recorded in the corresponding bit of the DBSR and causes the instruction execution to be suppressed. The

processor then enters the stop state and ceases the processing of instructions. The program counter will

contain the address of the instruction which caused the IAC debug event. Similarly, when operating in internal

debug mode with Debug interrupts enabled (MSR[DE] = 1), the occurrence of an IAC debug event is

recorded in the DBSR and causes the instruction execution to be suppressed. A Debug interrupt then occurs

with Critical Save/Restore Register 0 (CSRR0) set to the address of the instruction which caused the IAC

debug event.

When operating in internal debug mode (and not also in external debug mode nor debug wait mode) with

Debug interrupts disabled (MSR[DE] = 0), the behavior of IAC debug events depends on the IAC mode. If the

IAC mode is set to exact comparison, then an IAC debug event can occur and will set the corresponding IAC

field of the DBSR, along with the Imprecise Debug Event (IDE) field of the DBSR. The instruction execution is

not suppressed, as no Debug interrupt will occur immediately. Instead, instruction execution continues, and a

Debug interrupt will occur if and when MSR[DE] is set to 1, thereby enabling Debug interrupts, assuming soft-

ware has not cleared the IAC debug event status from the DBSR in the meantime. Upon such a “delayed”

interrupt, the Debug interrupt handler software may query the DBSR[IDE] field to determine that the Debug

Table 8-2. IAC Range Mode Auto-Toggle Summary

DBCR1 DBCR1 DBSR

IAC Mode

IAC12M/IAC34M IAC12AT/IAC34AT IAC12ATS/IAC34ATS

0b10 0 — Range Inclusive

0b10 1 0 Range Inclusive

0b10 1 1 Range Exclusive

0b11 0 — Range Exclusive

0b11 1 0 Range Exclusive

0b11 1 1 Range Inclusive