User’s Manual

Preliminary PPC440x5 CPU Core

intrupts.fm.

September 12, 2002

Page 171 of 589

Figure 6-8 shows the IVOR field definitions, while Table 6-1 identifies the specfic IVOR register associated

with each interrupt type.

6.4.10 Interrupt Vector Prefix Register (IVPR)

The IVPR provides the high-order 16 bits of the effective address of the interrupt vectors, for all interrupt

types. The interrupt vector effective address is formed as follows:

IVPR

0:15

|| IVORn

16:27

|| 0b0000

where n specifies the IVOR register to be used for the particular interrupt type.

The IVPR can be written from a GPR using mtspr, and can be read into a GPR using mfspr.

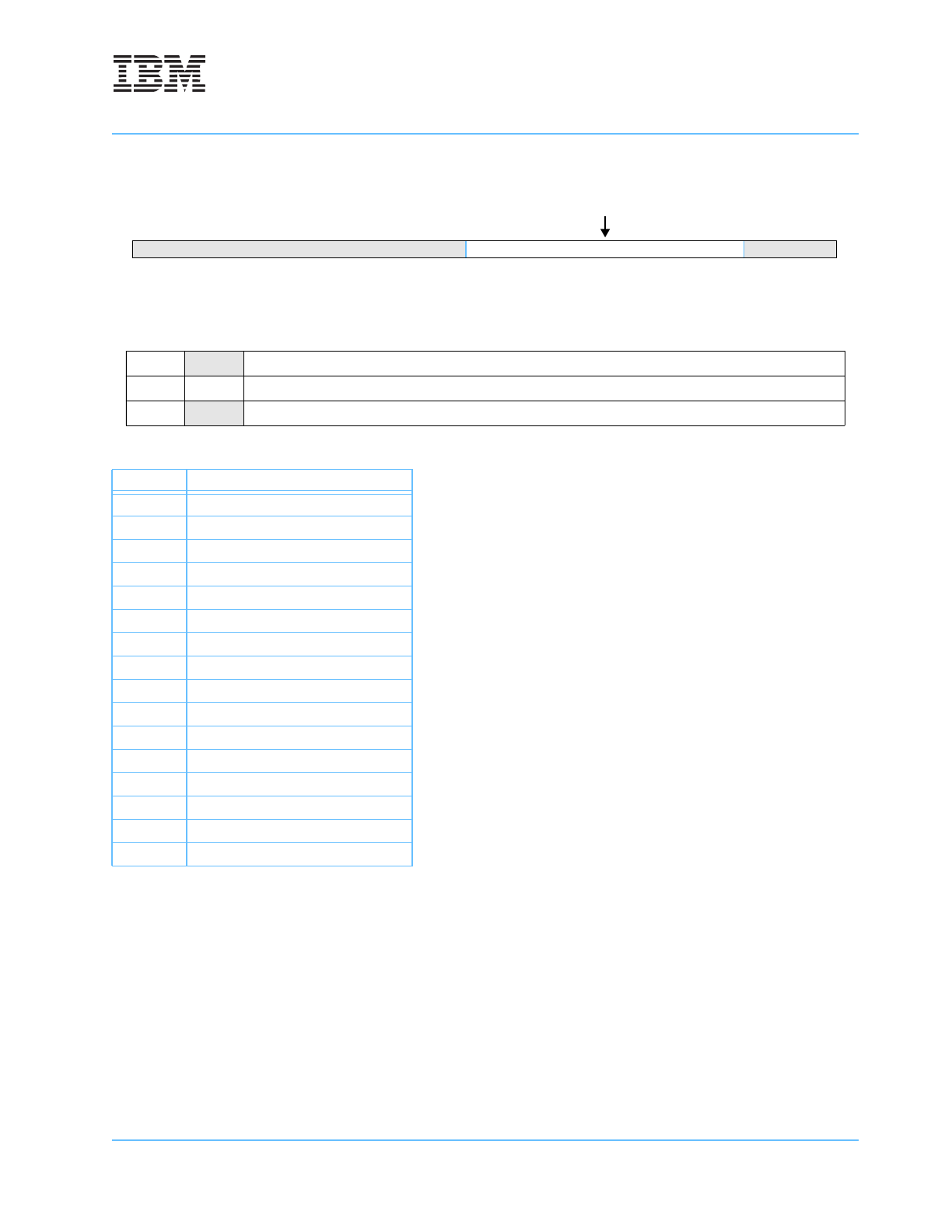

Figure 6-8. Interrupt Vector Offset Registers (IVOR0–IVOR15)

0:15 Reserved

16:27 IVO Interrupt Vector Offset

28:31

Reserved

Table 6-1. Interrupt Types Associated with each IVOR

IVOR Interrupt Type

IVOR0 Critical Input

IVOR1 Machine Check

IVOR2 Data Storage

IVOR3 Instruction Storage

IVOR4 External Input

IVOR5 Alignment

IVOR6 Program

IVOR7 Floating Point Unavailable

IVOR8 System Call

IVOR9 Auxiliary Processor Unavailable

IVOR10 Decrementer

IVOR11 Fixed Interval Timer

IVOR12 Watchdog Timer

IVOR13 Data TLB Error

IVOR14 Instruction TLB Error

IVOR15 Debug

0 15 16 27 28 31

IVO