User’s Manual

Preliminary PPC440x5 CPU Core

mmu.fm.

September 12, 2002

Page 137 of 589

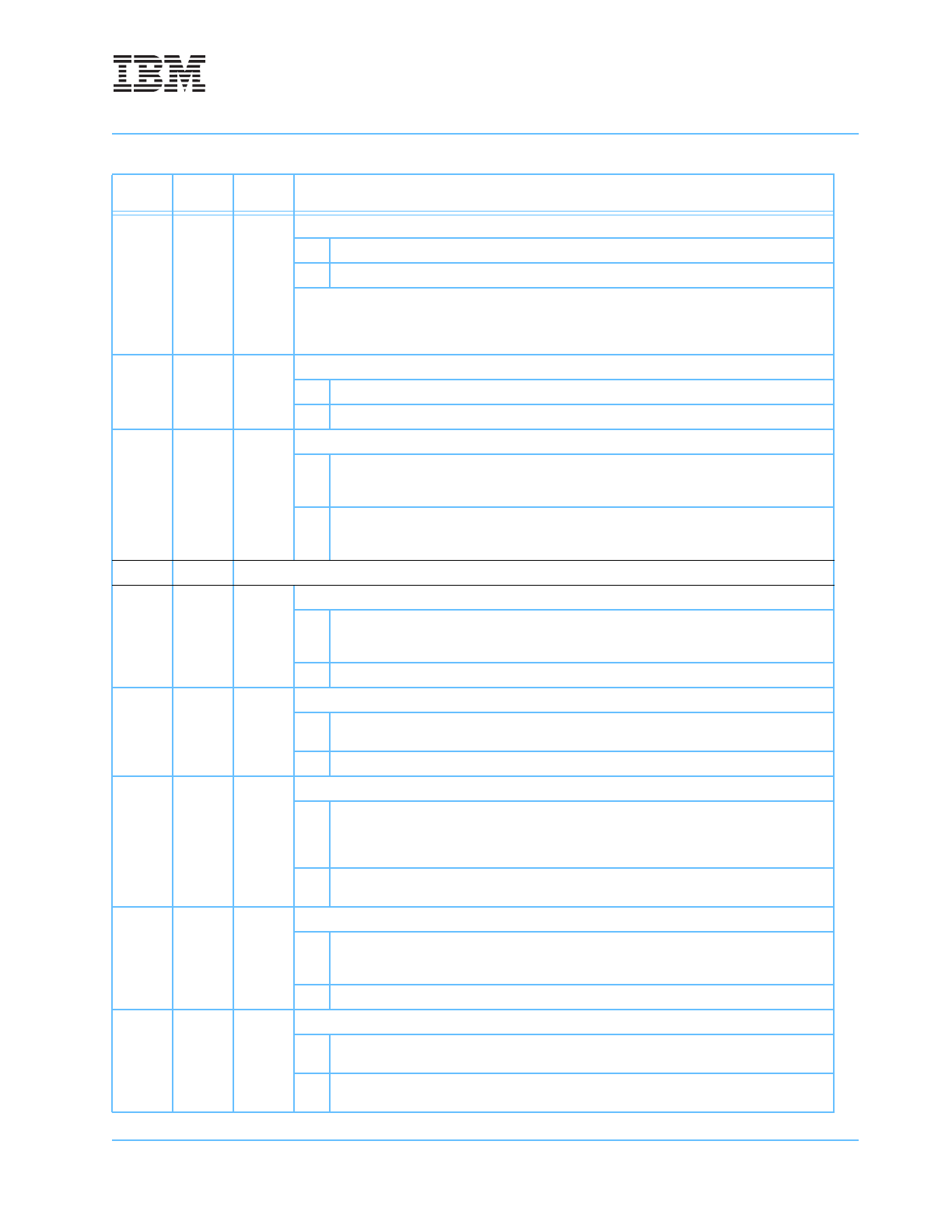

222M

Memory Coherence Required (1 bit) See Memory Coherence Required (M) on page 146.

0 The page is not memory coherence required.

1 The page is memory coherence required.

Note that the PPC440x5 does not support multiprocessing, and thus all storage accesses will

behave as if M=0. Setting M=1 in a TLB entry has no effect other than to cause any system inter-

face transactions to the corresponding page to be indicated as memory coherence required via

the “transfer attributes” interface signals.

223G

Guarded (1 bit) See Guarded (G) on page 146.

0 The page is not guarded.

1 The page is guarded.

224E

Endian (1 bit) See Endian (E) on page 146.

0

All accesses to the page are performed with big-endian byte ordering, which means that

the byte at the effective address is considered the most-significant byte of a multi-byte sca-

lar (see Byte Ordering on page 42).

1

All accesses to the page are performed with little-endian byte ordering, which means that

the byte at the effective address is considered the least-significant byte of a multi-byte sca-

lar (see Byte Ordering on page 42).

Access Control Fields

226UX

User State Execute Enable (1 bit) See Execute Access on page 142.

0

Instruction fetch is not permitted from this page while MSR[PR]=1 and the attempt to exe-

cute an instruction from this page while MSR[PR] =1 will cause an Execute Access Control

exception type Instruction Storage interrupt.

1 Instruction fetch and execution is permitted from this page while MSR[PR]=1.

227UW

User State Write Enable (1 bit) See Write Access on page 142.

0

Store operations and the dcbz instruction are not permitted to this page when MSR[PR]=1

and will cause a Write Access Control exception type Data Storage interrupt.

1 Store operations and the dcbz instruction are permitted to this page when MSR[PR]=1.

228UR

User State Read Enable (1 bit) See Read Access on page 143.

0

Load operations and the dcbt, dcbtst, dcbst, dcbf, icbt, and icbi instructions are not per-

mitted from this page when MSR[PR]=1 and will cause a Read Access Control exception.

Except for the dcbt, dcbtst, and icbt instructions, a Data Storage interrupt will occur (see

Table 5-4 on page 144).

1

Load operations and the dcbt, dcbtst, dcbst, dcbf, icbt, and icbi instructions are permit-

ted from this page when MSR[PR]=1.

229SX

Supervisor State Execute Enable (1 bit) See Execute Access on page 142.

0

Instruction fetch is not permitted from this page while MSR[PR]=0 and the attempt to exe-

cute an instruction from this page while MSR[PR] =0 will cause an Execute Access Control

exception type Instruction Storage interrupt.

1 Instruction fetch and execution is permitted from this page while MSR[PR]=0.

230SW

Supervisor State Write Enable (1 bit) See Write Access on page 142.

0

Store operations and the dcbz and dcbi instructions are not permitted to this page when

MSR[PR]=0 and will cause a Write Access Control exception type Data Storage interrupt.

1

Store operations and the dcbz and dcbi instructions are permitted to this page when

MSR[PR]=0.

Table 5-1. TLB Entry Fields (continued)

TLB

Word

Bit Field Description