User’s Manual

PPC440x5 CPU Core Preliminary

Page 30 of 589

overview.fm.

September 12, 2002

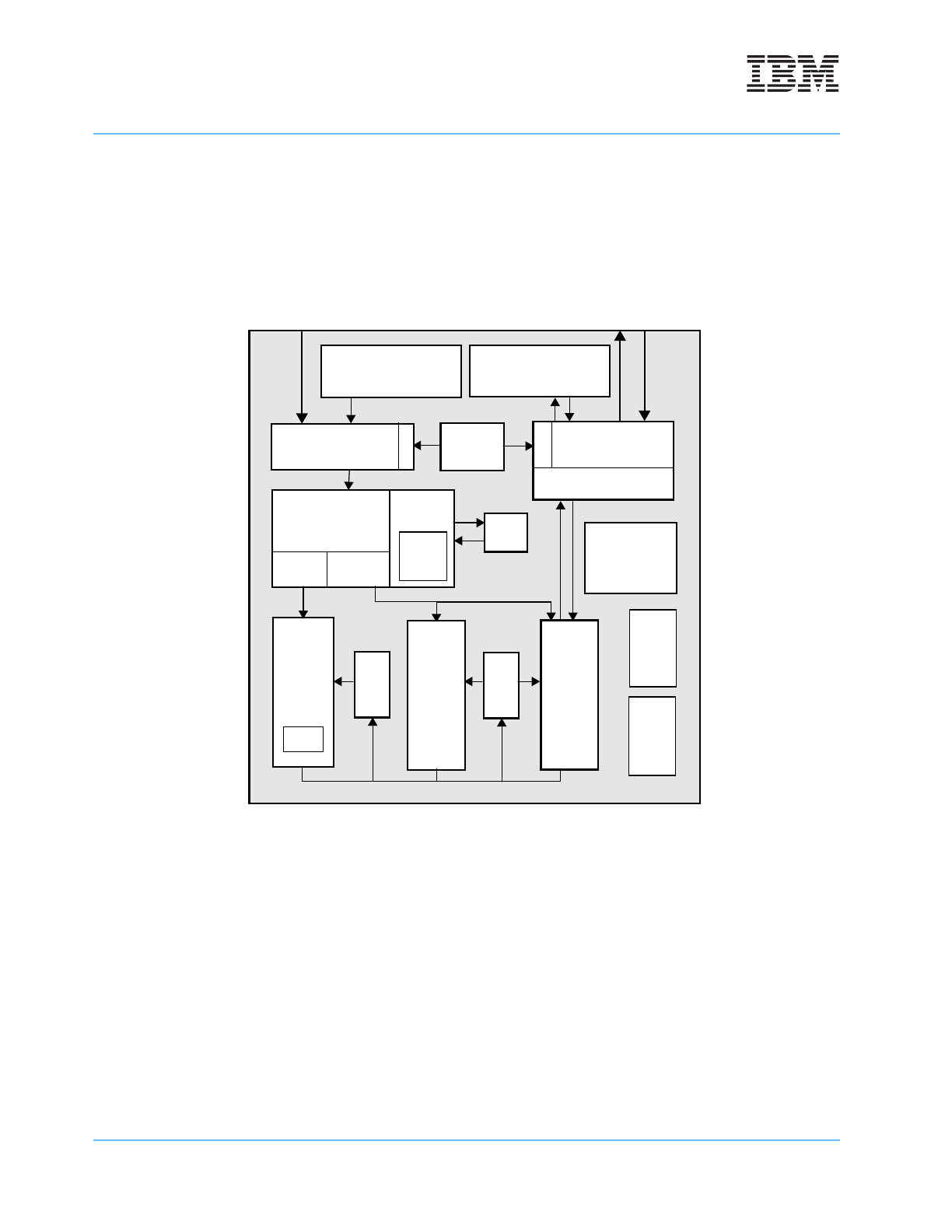

1.3 PPC440x5 Organization

The PPC440x5 core includes a seven-stage pipelined PowerPC core, which consists of a three stage, dual-

issue instruction fetch and decode unit with attached branch unit, together with three independent, 4-stage

pipelines for complex integer, simple integer, and load/store operations, respectively. The PPC440x5 core

also includes a memory management unit (MMU); separate instruction and data cache units; JTAG, debug,

and trace logic; and timer facilities.

Figure 1-1 illustrates the logical organization of the PPC440x5 core:

1.3.1 Superscalar Instruction Unit

The instruction unit of the PPC440x5 core fetches, decodes, and issues two instructions per cycle to any

combination of the three execution pipelines and/or the APU interface (see “Execution Pipelines” below, and

Auxiliary Processor Unit (APU) Port on page 36). The instruction unit includes a branch unit which provides

dynamic branch prediction using a branch history table (BHT), as well as a branch target address cache

(BTAC). These mechanisms greatly improve the branch prediction accuracy and reduce the latency of taken

branches, such that the target of a branch can usually be executed immediately after the branch itself, with no

penalty.

MAC

BHT

4KB

Instruction Cache

Branch

Instruction

Unit

D-Cache Controller

Load/Store Queues

I-Cache Controller

(Size Configurable)

Data Cache

MMU

64-entry

Pwr Mgmt

Clocks

Unit

Target

Addr

Cache

1

0

and

ITLB

DTLB

GPR

File

(Size Configurable)

128-bit

PLB

128-bit

PLB

Simple

Integer

Pipe

Complex

Integer

Pipe

Issue Issue

Load

Store

Pipe

Figure 1-1. PPC440 Core Block Diagram

GPR

File

DCR Bus

Trace

Debug

JTAG

Timers

Interrupt

and