DBCR1

Debug Control Register 1

Preliminary PPC440x5 CPU Core User’s Manual

regsumm440core.fm.

September 12, 2002 Page 471 of 589

DBCR1

SPR 0x135 Supervisor R/W

See Debug Control Register 1 (DBCR1) on page 240.

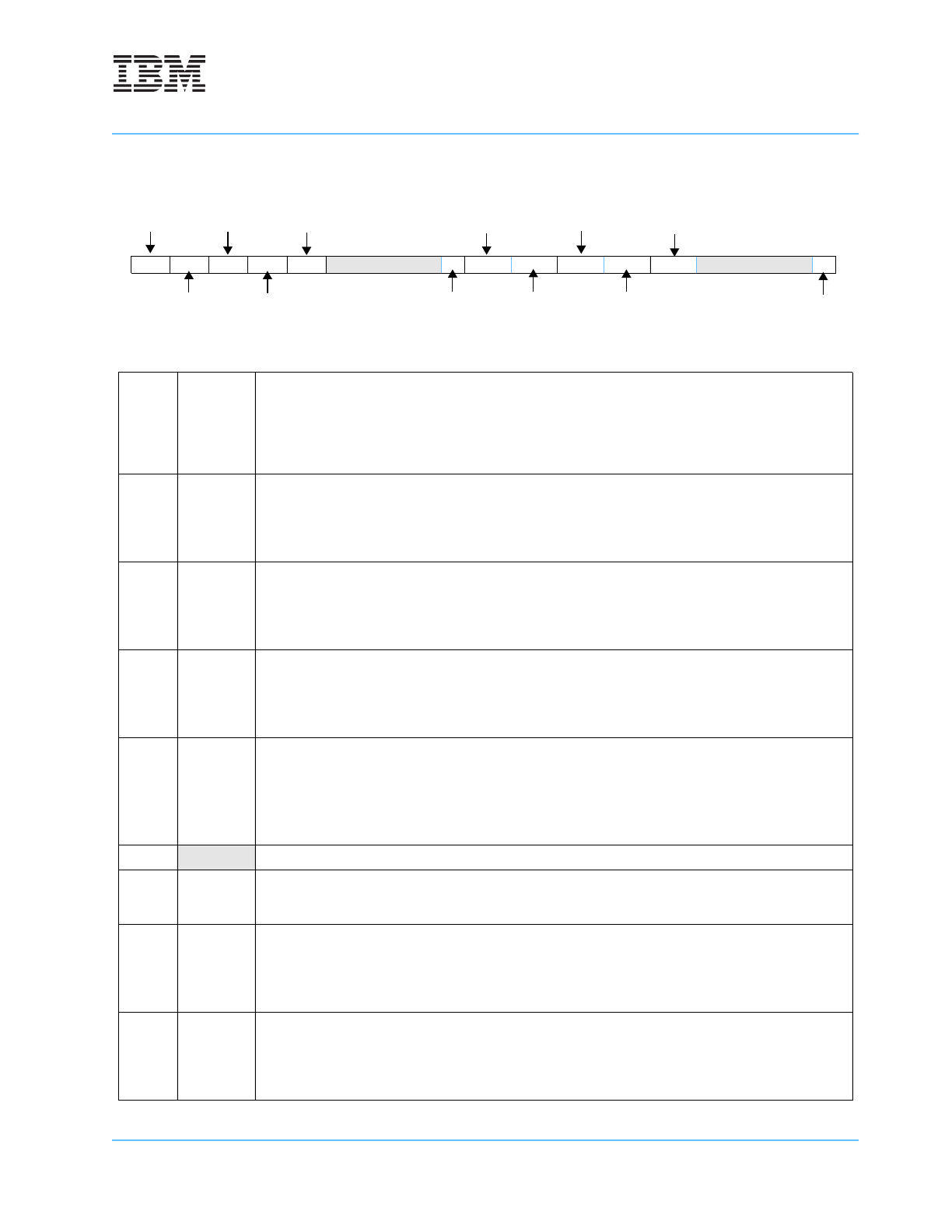

Figure 10-9. Debug Control Register 1 (DBCR1)

0:1 IAC1US

Instruction Address Compare (IAC) 1 User/Super-

visor

00 Both

01 Reserved

10 Supervisor only (MSR[PR] = 0)

11 User only (MSR[PR] = 1)

2:3 IAC1ER

IAC 1 Effective/Real

00 Effective (MSR[IS] = don’t care)

01 Reserved

10 Virtual (MSR[IS] = 0)

11 Virtual (MSR[IS] = 1)

4:5 IAC2US

IAC 2 User/Supervisor

00 Both

01 Reserved

10 Supervisor only (MSR[PR] = 0)

11 User only (MSR[PR] = 1)

6:7 IAC2ER

IAC 2 Effective/Real

00 Effective (MSR[IS] = don’t care)

01 Reserved

10 Virtual (MSR[IS] = 0)

11 Virtual (MSR[IS] = 1)

8:9 IAC12M

IAC 1/2 Mode

00 Exact match

01 Reserved

10 Range inclusive

11 Range exclusive

Match if address[0:29] = IAC 1/2[0:29]; two inde-

pendent compares

Match if IAC1

≤ address < IAC2

Match if address < IAC1 OR address ≥ IAC2

10:14 Reserved

15 IAC12AT

IAC 1/2 Auto-Toggle Enable

0 Disable IAC 1/2 auto-toggle

1 Enable IAC 1/2 auto-toggle

16:17 IAC3US

IAC 3 User/Supervisor

00 Both

01 Reserved

10 Supervisor only (MSR[PR] = 0)

11 User only (MSR[PR] = 1)

18:19 IAC3ER

IAC 3 Effective/Real

00 Effective (MSR[IS] = don’t care)

01 Reserved

10 Virtual (MSR[IS] = 0)

11 Virtual (MSR[IS] = 1)

012345678910 14 15 16 17 18 19 20 21 22 23 24 25 26 30 31

IAC1US

IAC1ER

IAC2US

IAC12M

IAC12AT

IAC3US

IAC3ER

IAC4US

IAC34M

IAC4ER

IAC34A

T

IAC2ER