User’s Manual

PPC440x5 CPU Core Preliminary

Page 216 of 589

timers.fm.

September 12, 2002

7.6 Timer Status Register (TSR)

The TSR is a privileged SPR that records the status of DEC, FIT, and Watchdog Timer events. The fields of

the TSR are generally set to 1 only by hardware and cleared to 0 only by software. Hardware cannot clear

any fields in the TSR, nor can software set any fields. Software can read the TSR into a GPR using mfspr.

Clearing the TSR is performed using mtspr by placing a 1 in the GPR source register in all bit positions which

are to be cleared in the TSR, anda0inallother bit positions. The data written from the GPR to the TSR is not

direct data, but a mask. A 1 clears the bit and a 0 leaves the corresponding TSR bit unchanged.

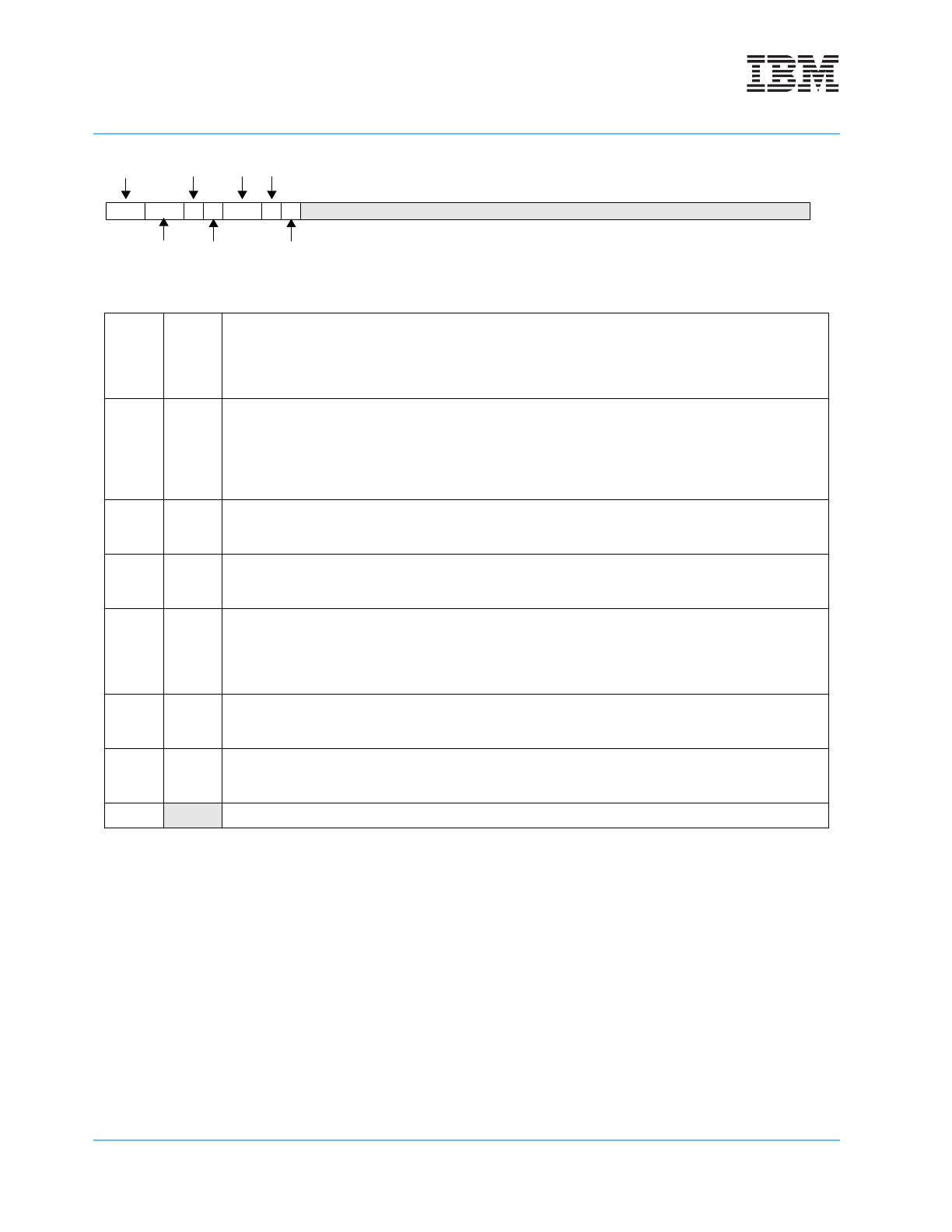

Figure 7-7. Timer Control Register (TCR)

0:1 WP

Watchdog Timer Period

00 2

21

time base clocks

01 2

25

time base clocks

10 2

29

time base clocks

11 2

33

time base clocks

2:3 WRC

Watchdog Timer Reset Control

00 No Watchdog Timer reset will occur.

01 Core reset

10 Chip reset

11 System reset

TCR[WRC] resets to 0b00.

Type of reset to cause upon Watchdog Timer excep-

tion with TSR[ENW,WIS]=0b11.

This field can be set by software, but cannot be

cleared by software, except by a software-induced

reset.

4 WIE

Watchdog Timer Interrupt Enable

0 Disable Watchdog Timer interrupt.

1 Enable Watchdog Timer interrupt.

5

DIE

Decrementer Interrupt Enable

0 Disable Decrementer interrupt.

1 Enable Decrementer interrupt.

6:7 FP

Fixed Interval Timer (FIT) Period

00 2

13

time base clocks

01 2

17

time base clocks

10 2

21

time base clocks

11 2

25

time base clocks

8 FIE

FIT Interrupt Enable

0 Disable Fixed Interval Timer interrupt.

1 Enable Fixed Interval Timer interrupt.

9 ARE

Auto-Reload Enable

0 Disable auto reload.

1 Enable auto reload.

TCR[ARE] resets to 0b0.

10:31 Reserved

012345678910 31

WP

WRC

WIE

DIE

FP FIE

ARE