User’s Manual

Preliminary PPC440x5 CPU Core

intrupts.fm.

September 12, 2002

Page 165 of 589

Decrementer

Fixed-Interval Timer

Watchdog Timer

Debug (Unconditional Debug Event)

2. Unaligned elementary load or store, or any load or store multiple or string:

All of the above listed under item 1, plus the following:

Alignment

Data Storage (if the access crosses a memory page boundary)

Debug (Data Address Compare, Data Value Compare)

6.4 Interrupt Processing Registers

The interrupt processing registers include the Save/Restore Registers (SRR0–SRR1), Critical Save/Restore

Registers (CSRR0–CSRR1), Data Exception Address Register (DEAR), Interrupt Vector Offset Registers

(IVOR0–IVOR15), Interrupt Vector Prefix Register (IVPR), and Exception Syndrome Register (ESR). Also

described in this section is the Machine State Register (MSR), which belongs to the category of processor

control registers.

6.4.1 Machine State Register (MSR)

The MSR is a register of its own unique type that controls important chip functions, such as the enabling or

disabling of various interrupt types.

The MSR can be written from a GPR using the mtmsr instruction. The contents of the MSR can be read into

a GPR using the mfmsr instruction. The MSR[EE] bit can be set or cleared atomically using the wrtee or

wrteei instructions. The MSR contents are also automatically saved, altered, and restored by the interrupt-

handling mechanism.

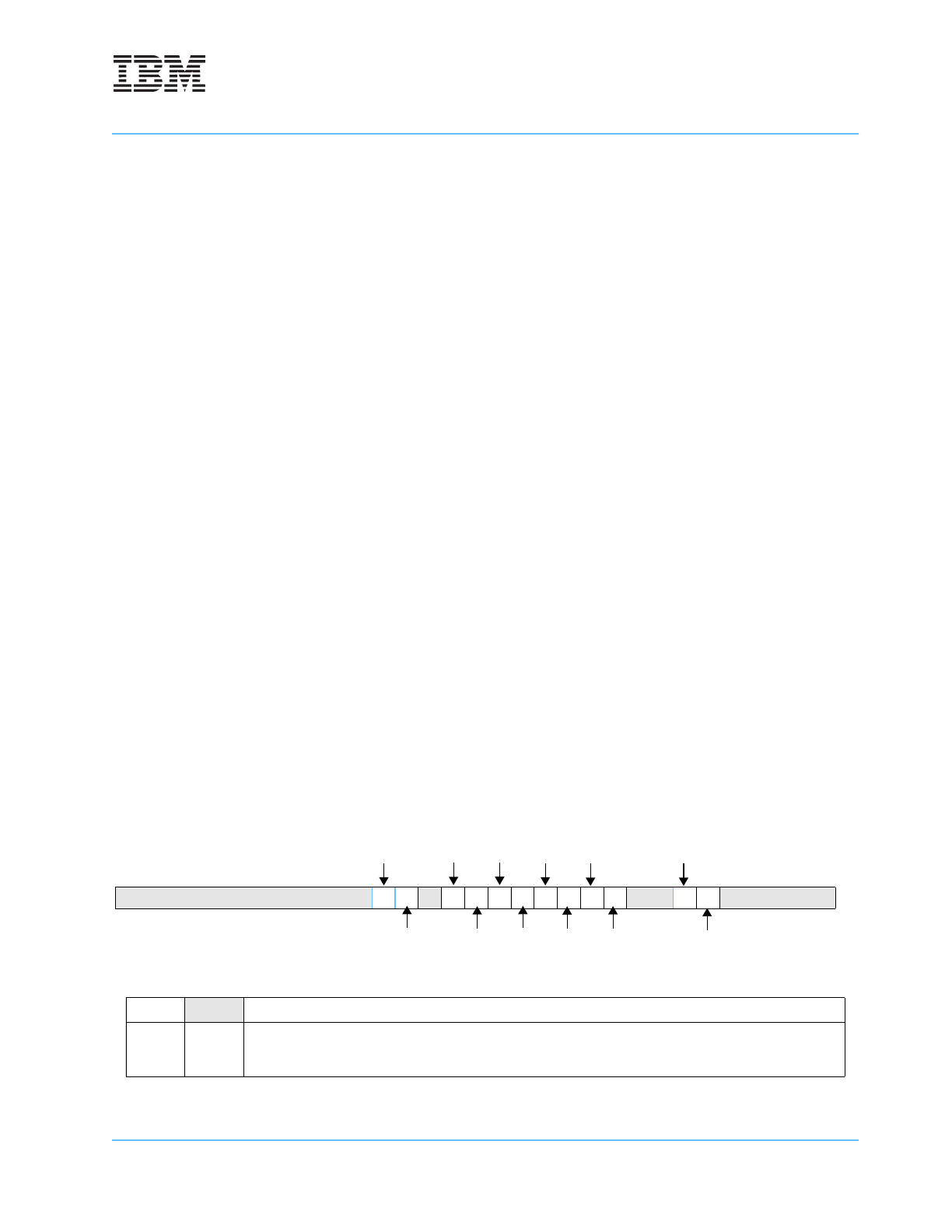

Figure 6-1 shows the MSR bit definitions and describes the function of each bit.

Figure 6-1. Machine State Register (MSR)

0:12 Reserved

13 WE

Wait State Enable

0 The processor is not in the wait state.

1 The processor is in the wait state.

If MSR[WE] = 1, the processor remains in the wait

state until an interrupt is taken, a reset occurs, or

an external debug tool clears WE.

0 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 31

FE1

WE

PR

DS

CE

EE

DE

FP

ME

DWE

FE0

IS