User’s Manual

PPC440x5 CPU Core Preliminary

Page 238 of 589

debug.fm.

September 12, 2002

8.4 Debug Reset

Software can initiate an immediate reset operation by setting DBCR0[RST] to a non-zero value. The results of

a reset operation within the PPC440x5 core are described in Initialization on page 85. The results of a reset

operation on the rest of the chip and/or system is dependent on the particular type of reset operation (core,

chip, or system reset), and on the particular chip and system implementation. See the chip user’s manual for

details.

8.5 Debug Timer Freeze

In order to maintain the semblance of “real time” operation while a system is being debugged, DBCR0[FT]

can be set to 1, which will cause all of the timers within the PPC440x5 core to stop incrementing or decre-

menting for as long as a debug event bit is set in the DBSR, or until DBCR0[FT] is set to 0. See Timer Facili-

ties on page 209 for more information on the operation of the PPC440x5 core timers.

8.6 Debug Registers

Various Special Purpose Registers (SPRs) are used to enable the debug modes, to configure and record

debug events, and to communicate with debug tool hardware and software. These debug registers may be

accessed either through software running on the processor or through the JTAG debug port of the

PPC440x5.

Programming Note: It is the responsibility of software to synchronize the context of any

changes to the debug facility registers. Specifically, when changing the

contents of any of the debug facility registers, software must execute an

isync instruction both before and after the changes to these registers, to

ensure that all preceding instructions use the old values of the registers,

and that all succeeding instructions use the new values. In addition, when

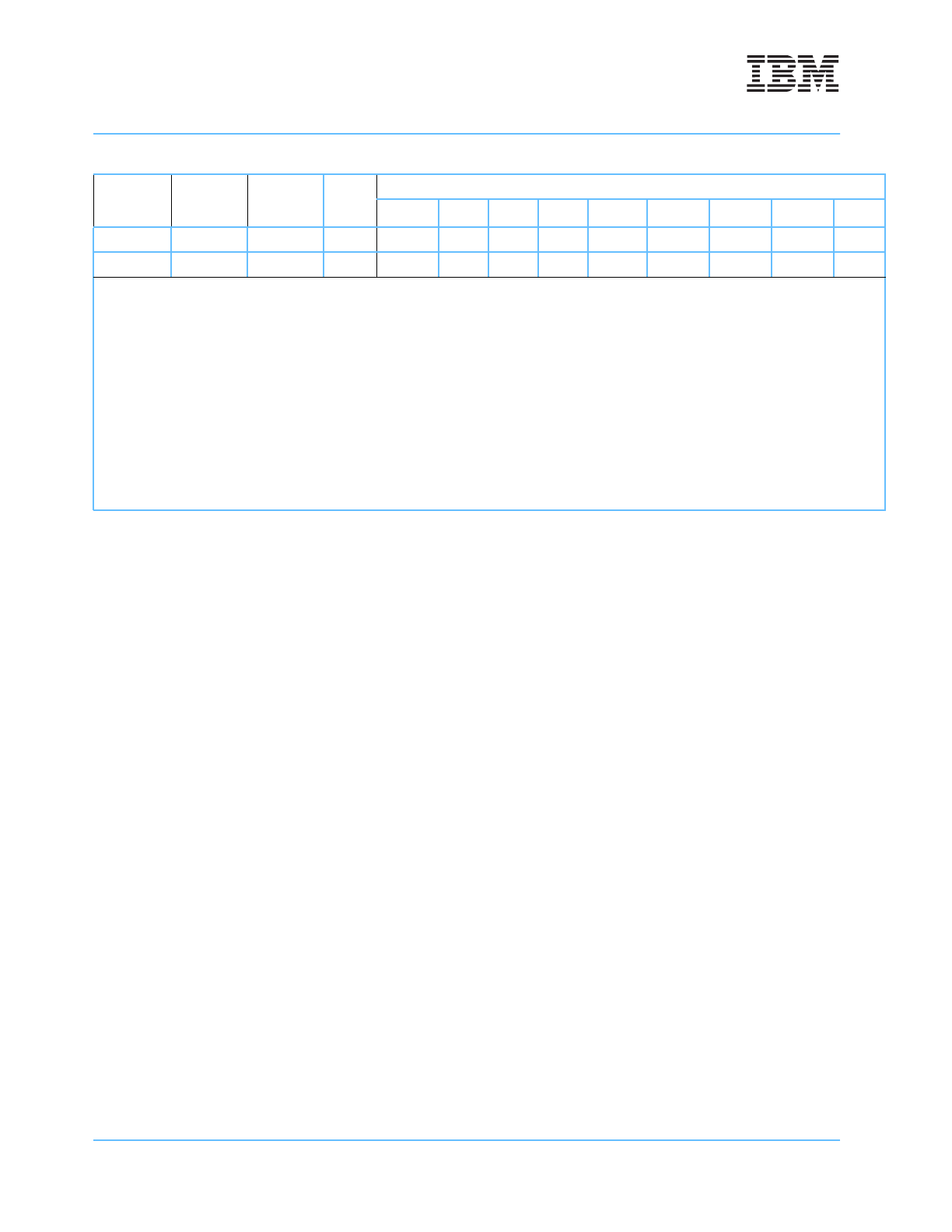

Disabled Disabled Enabled 0 Note 2 Yes Yes No Yes Note 3 No Note 1 Yes

Disabled Disabled Disabled — Yes Yes Yes Yes Yes Yes Note 4 yes Yes

Table Notes

1. IRPT debug events may only occur for non-critical class interrupts when operating in internal debug mode with

external debug mode and debug wait mode both disabled.

2. IAC debug events may not occur in internal debug mode with MSR[DE] = 0 and with external debug mode

and debug wait mode both disabled, and the IAC mode set to range inclusive or range exclusive. They may

occur if the IAC mode is set to exact.

3. RET debug events may not occur for rfci or rfmci instructions when operating in internal debug mode with

MSR[DE] = 0 and with external debug mode and debug wait mode both disabled. They may only occur in this

mode for the rfi instruction.

4. ICMP debug events are not permitted when operating in trace debug mode. Software must not enable ICMP

debug events unless one of the other debug modes is enabled.

Table 8-3. Debug Event Summary (continued)

External

Debug

Mode

Debug

Wait

Mode

Internal

Debug

Mode

MSR

DE

Debug Events

IAC DAC DVC BRT TRAP RET ICMP IRPT UDE