ESR

Exception Syndrome Register

Preliminary PPC440x5 CPU Core User’s Manual

regsumm440core.fm.

September 12, 2002 Page 487 of 589

ESR

SPR 0x03E Supervisor R/W

See Exception Syndrome Register (ESR) on page 172.

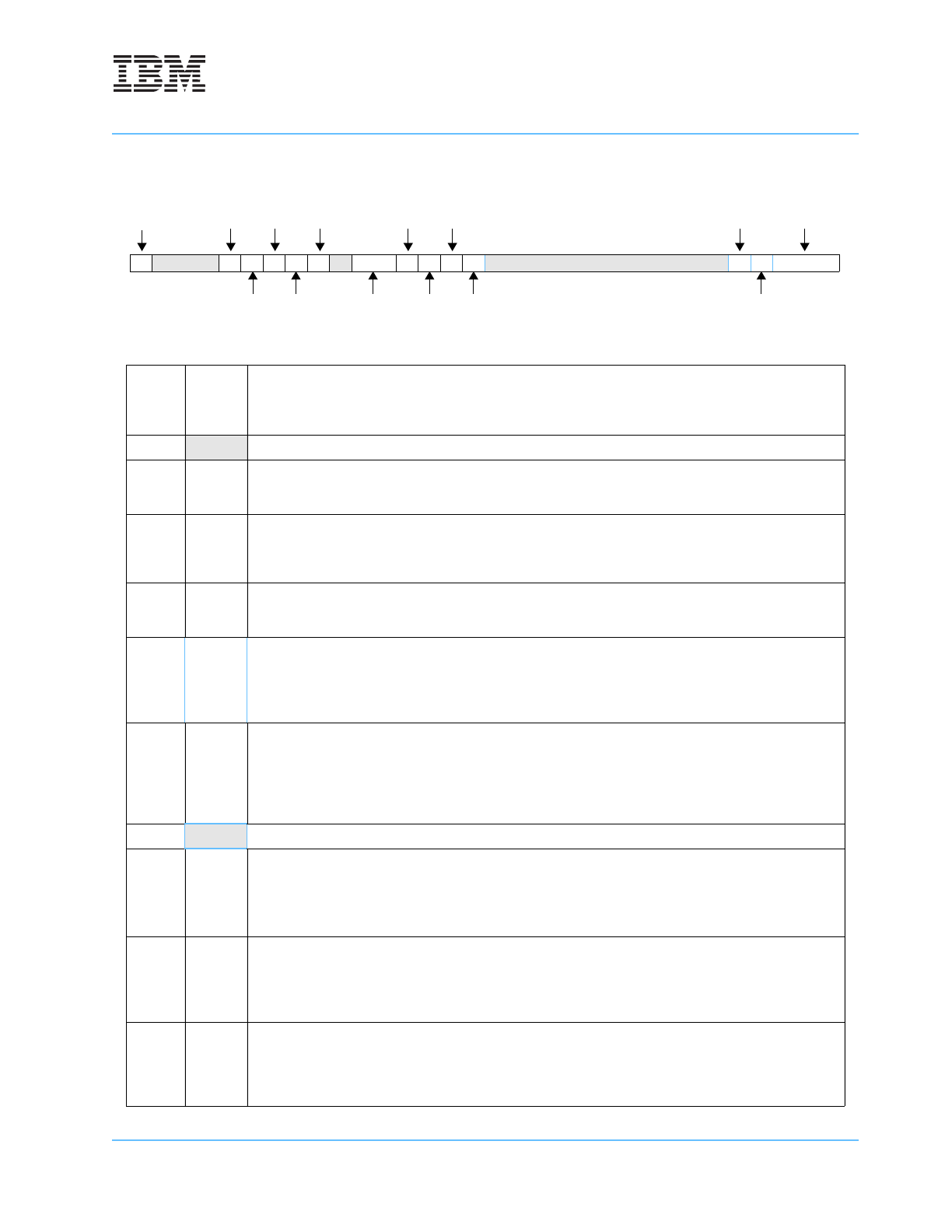

Figure 10-22. Exception Syndrome Register (ESR)

0 MCI

Machine Check—Instruction Fetch Exception

0 Instruction Machine Check exception did not

occur.

1 Instruction Machine Check exception occurred.

This is an implementation-dependent field of the

ESR and is not part of the PowerPC Book-E Archi-

tecture.

1:3 Reserved

4 PIL

Program Interrupt—Illegal Instruction Exception

0 Illegal Instruction exception did not occur.

1 Illegal Instruction exception occurred.

5 PPR

Program Interrupt—Privileged Instruction Excep-

tion

0 Privileged Instruction exception did not occur.

1 Privileged Instruction exception occurred.

6 PTR

Program Interrupt—Trap Exception

0 Trap exception did not occur.

1 Trap exception occurred.

7

FP

Floating Point Operation

0 Exception was not caused by a floating point

instruction.

1 Exception was caused by a floating point

instruction.

8ST

Store Operation

0 Exception was not caused by a store-type

storage access or cache management

instruction.

1 Exception was caused by a store-type storage

access or cache management instruction.

9 Reserved

10:11 DLK

Data Storage Interrupt—Locking Exception

00 Locking exception did not occur.

01 Locking exception was caused by dcbf.

10 Locking exception was caused by icbi.

11 Reserved

12 AP

AP Operation

0 Exception was not caused by an auxiliary

processor instruction.

1 Exception was caused by an auxiliary processor

instruction.

13 PUO

Program Interrupt—Unimplemented Operation

Exception

0 Unimplemented Operation exception did not

occur.

1 Unimplemented Operation exception occurred.

0 1 3456789 10111213141516 26 27 28 29 31

MCI PIL

PPR

PTR

FP

DLK

AP

PUO

BO

ST

PIE

PCRE PCRF

PCMP