User’s Manual

PPC440x5 CPU Core Preliminary

Page 138 of 589

mmu.fm.

September 12, 2002

5.3 Page Identification

The Valid (V), Effective Page Number (EPN), Translation Space Identifier (TS), Page Size (SIZE), and Trans-

lation ID (TID) fields of a particular TLB entry identify the page associated with that TLB entry. Except as

noted, all comparisons must succeed to validate this entry for subsequent translation and access control

processing. Failure to locate a matching TLB entry based on this criteria for instruction fetches will result in a

TLB Miss exception type Instruction TLB Error interrupt. Failure to locate a matching TLB entry based on this

criteria for data storage accesses will result in a TLB Miss exception which may result in a Data TLB Error

interrupt, depending on the type of data storage access (certain cache management instructions do not result

in an interrupt if they cause an exception; they simply no-op).

5.3.1 Virtual Address Formation

The first step in page identification is the expansion of the effective address into a virtual address. Again, the

effective address is the 32-bit address calculated by a load, store, or cache management instruction, or as

part of an instruction fetch. The virtual address is formed by prepending the effective address with a 1-bit

address space identifier and an 8-bit process identifier. The process identifier is contained in the Process ID

(PID) register. The address space identifier is provided by MSR[IS] for instruction fetches, and by MSR[DS]

for data storage accesses and cache management operations, including instruction cache management

operations. The resulting 41-bit value forms the virtual address, which is then compared to the virtual

addresses contained in the TLB entries.

Note that the tlbsx[.] instruction also forms a virtual address, for software controlled search of the TLB. This

instruction calculates the effective address in the same manner as a data access instruction, but the process

identifier and address space identifier are provided by fields in the MMUCR, rather than by the PID and MSR,

respectively (see TLB Search Instruction (tlbsx[.]) on page 153).

5.3.2 Address Space Identifier Convention

The address space identifier differentiates between two distinct virtual address spaces, one generally associ-

ated with interrupt-handling and other system-level code and/or data, and the other generally associated with

application-level code and/or data.

Typically, user mode programs will run with MSR[IS,DS] both set to 1, allowing access to application-level

code and data memory pages. Then, on an interrupt, MSR[IS,DS] are both automatically cleared to 0, so that

the interrupt handler code and data areas may be accessed using system-level TLB entries (that is, TLB

entries with the TS field = 0). It is also possible that an operating system could set up certain system-level

code and data areas (and corresponding TLB entries with the TS field = 1) in the application-level address

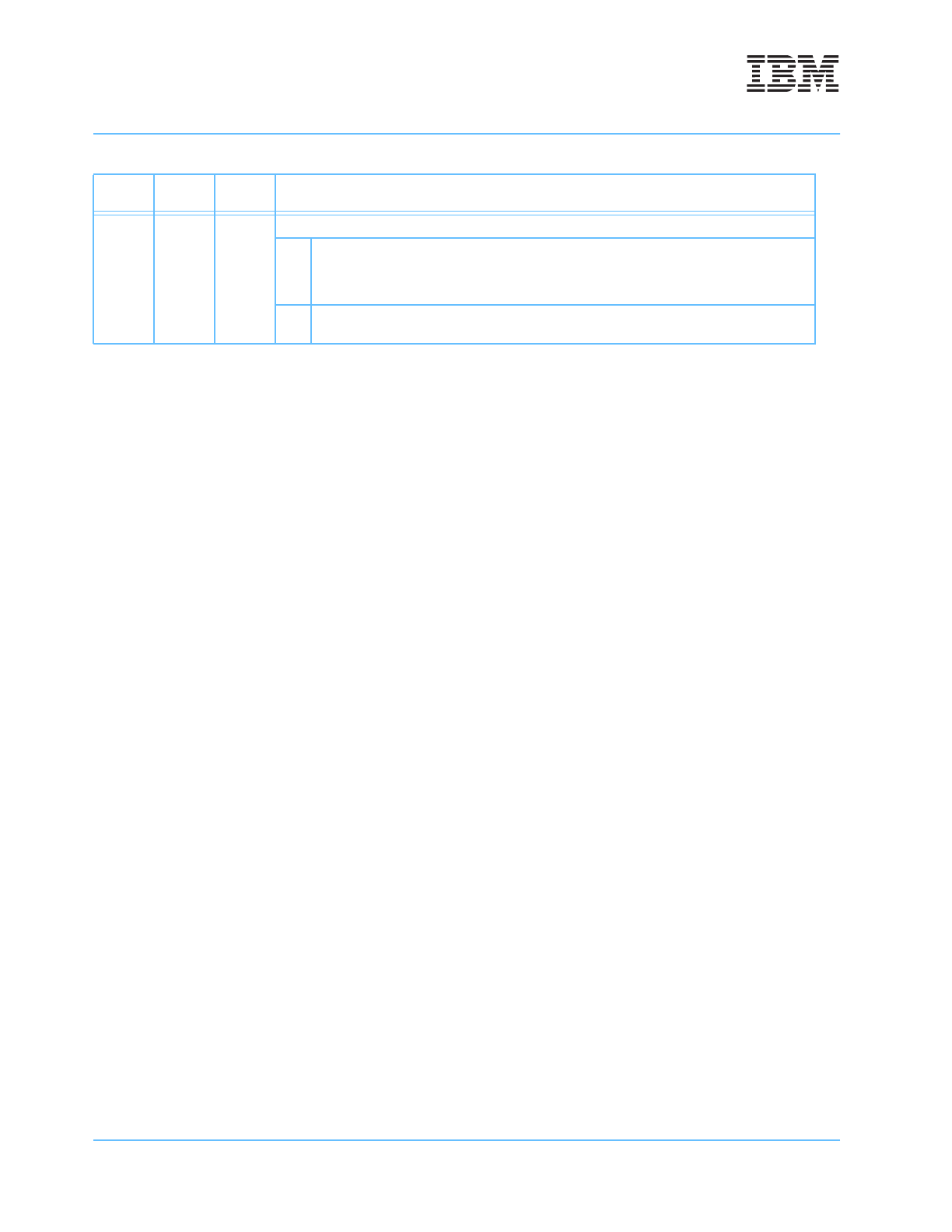

231SR

Supervisor State Read Enable (1 bit) See Read Access on page 143.

0

Load operations and the dcbt, dcbtst, dcbst, dcbf, icbt, and icbi instructions are not per-

mitted from this page when MSR[PR]=0 and will cause a Read Access Control exception.

Except for the dcbt, dcbtst, and icbt instructions, a Data Storage interrupt will occur (see

Table 5-4 on page 144).

1

Load operations and the dcbt, dcbtst, dcbst, dcbf, icbt, and icbi instructions are permit-

ted from this page when MSR[PR]=0.

Table 5-1. TLB Entry Fields (continued)

TLB

Word

Bit Field Description