User’s Manual

Preliminary PPC440x5 CPU Core

debug.fm.

September 12, 2002

Page 239 of 589

changing any of the debug facility register fields related to the DAC and/or

DVC debug events, software must execute an msync instruction before

making the changes, to ensure that all storage accesses complete using

the old context of these register fields.

8.6.1 Debug Control Register 0 (DBCR0)

DBCR0 is an SPR that is used to enable debug modes and events, reset the processor, and control timer

operation when debugging. DBCR0 can be written from a GPR using mtspr, and can be read into a GPR

using

mfspr.

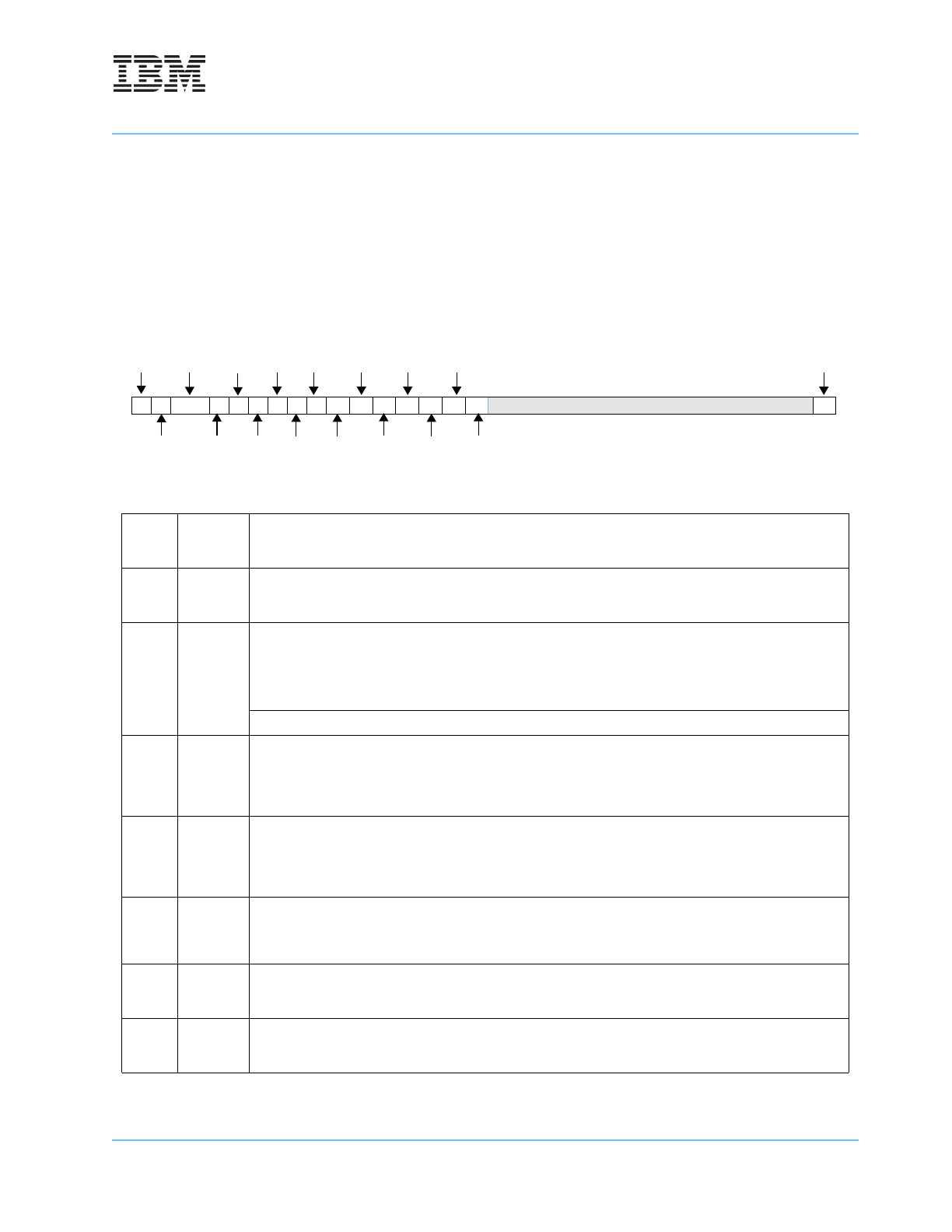

Figure 8-1. Debug Control Register 0 (DBCR0)

0 EDM

External Debug Mode

0 Disable external debug mode.

1 Enable external debug mode.

1 IDM

Internal Debug Mode

0 Disable internal debug mode.

1 Enable internal debug mode.

2:3 RST

Reset

00 No action

01 Core reset

10 Chip reset

11 System reset

Attention: Writing 01, 10, or 11 to this field causes a processor reset to occur.

4 ICMP

Instruction Completion Debug Event

0 Disable instruction completion debug event.

1 Enable instruction completion debug event.

Instruction completions do not cause

instruction completion debug events if

MSR[DE] = 0 in internal debug mode,

unless also in external debug mode or

debug wait mode.

5 BRT

Branch Taken Debug Event

0 Disable branch taken debug event.

1 Enable branch taken debug event.

Taken branches do not cause branch

taken debug events if MSR[DE] = 0 in

internal debug mode, unless also in

external debug mode or debug wait

mode.

6 IRPT

Interrupt Debug Event

0 Disable interrupt debug event.

1 Enable interrupt debug event.

Critical interrupts do notcause interrupt

debug events in internal debug mode,

unless also in external debug mode or

debug wait mode.

7 TRAP

Trap Debug Event

0 Disable trap debug event.

1 Enable trap debug event.

8 IAC1

Instruction Address Compare (IAC) 1 Debug Event

0 Disable IAC 1 debug event.

1 Enable IAC 1 debug event.

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 30 31

EDM

IDM

RST

ICMP

BRT

RETDAC1R

TRAP FT

IAC1

IAC2

IAC3

IAC4 DAC1W

DAC2RIRPT

DAC2W