User’s Manual

Preliminary PPC440x5 CPU Core

cache.fm.

September 12, 2002

Page 111 of 589

4.2.4.4 icbt Operation

The icbt instruction is typically used as a “hint” to the processor that a particular block of instructions is likely

to be executed in the near future. Thus the processor can begin filling that block into the instruction cache, so

that when the executing program eventually branches there the instructions will already be present in the

cache, thereby improving performance.

Of course, it would not typically be advantageous if the filling of the cache line requested by the icbt itself

caused a delay in the fetching of instructions needed by the currently executing program. For this reason, the

default behavior of the icbt instruction is for it to have the lowest priority for sending a request to the PLB. If a

subsequent instruction cache miss occurs due to a request from the instruction unit, then the line fill for the

icbt will be abandoned (if it has not already been acknowledged on the PLB).

On the other hand, the icbt instruction can also be used as a convenient mechanism for setting up a fixed,

known environment within the instruction cache. This is useful for establishing contents for cache line locking,

or for deterministic performance on a particular sequence of code, or even for debugging of low-level hard-

ware and software problems.

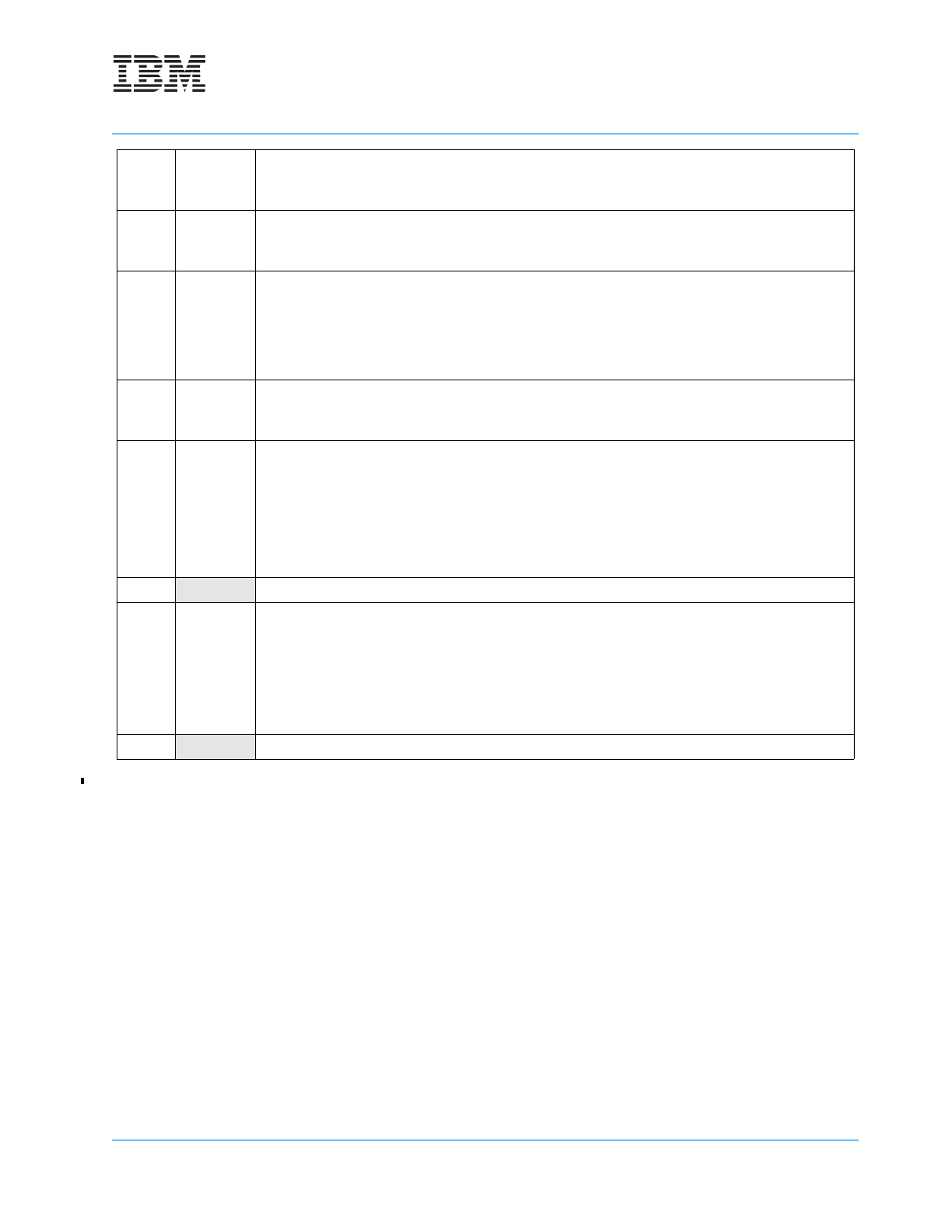

13 DCUPEI

Data Cache U-bit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bit recorded for the U

fields in the data cache.

14 DCMPEI

Data Cache Modified-bit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of parity bits recorded for the

modified (dirty) field in the data cache.

15 FCOM

Force Cache Operation Miss

0 normal operation

1 cache ops appear to miss the cache

Force icbt , dcbt, dcbtst, dcbst, dcbf, dcbi, and

dcbz to appear to miss the caches. The intended

use is with icbt and dcbt only, which will fill a dupli-

cate line and allow testing of multi-hit parity errors.

See Section 4.2.4.7 Simulating Instruction Cache

Parity Errors for Software Testing on page 114 and

Figure 4.3.3.7 on page 130.

16:19 MMUPEI

Memory Management Unit Parity Error Insert

0 record even parity (normal)

1 record odd parity (simulate parity error)

Controls inversion of paritybits recordedfor the tag

field in the MMU.

20 FFF

Force Full-line Flush

0 flush only as much data as necessary.

1 always flush entire cache lines

When flushing 32-byte (8-word) lines from the data

cache, normal operation is to write nothing, a dou-

ble word, quad word, or the entire 8-word block to

the memory as required by the dirty bits. This bit

ensures that none or all dirty bits are set so that

either nothing or the entire 8-word block is written

to memory when flushing a line from the data

cache. Refer to Section 4.3.1.4 Line Flush Opera-

tions on page 121.

21:23 Reserved

24 TCS

Timer Clock Select

0 CPU timer advances by one at each

rising edge of the CPU input clock

(CPMC440CLOCK).

1 CPU timer advances by one for each

rising edge of the CPU timer clock

(CPMC440TIMERCLOCK).

When TCS = 1, CPU timer clock input can toggle

at up to half of the CPU clock frequency.

25:31 Reserved