User’s Manual

Preliminary PPC440x5 CPU Core

cache.fm.

September 12, 2002

Page 121 of 589

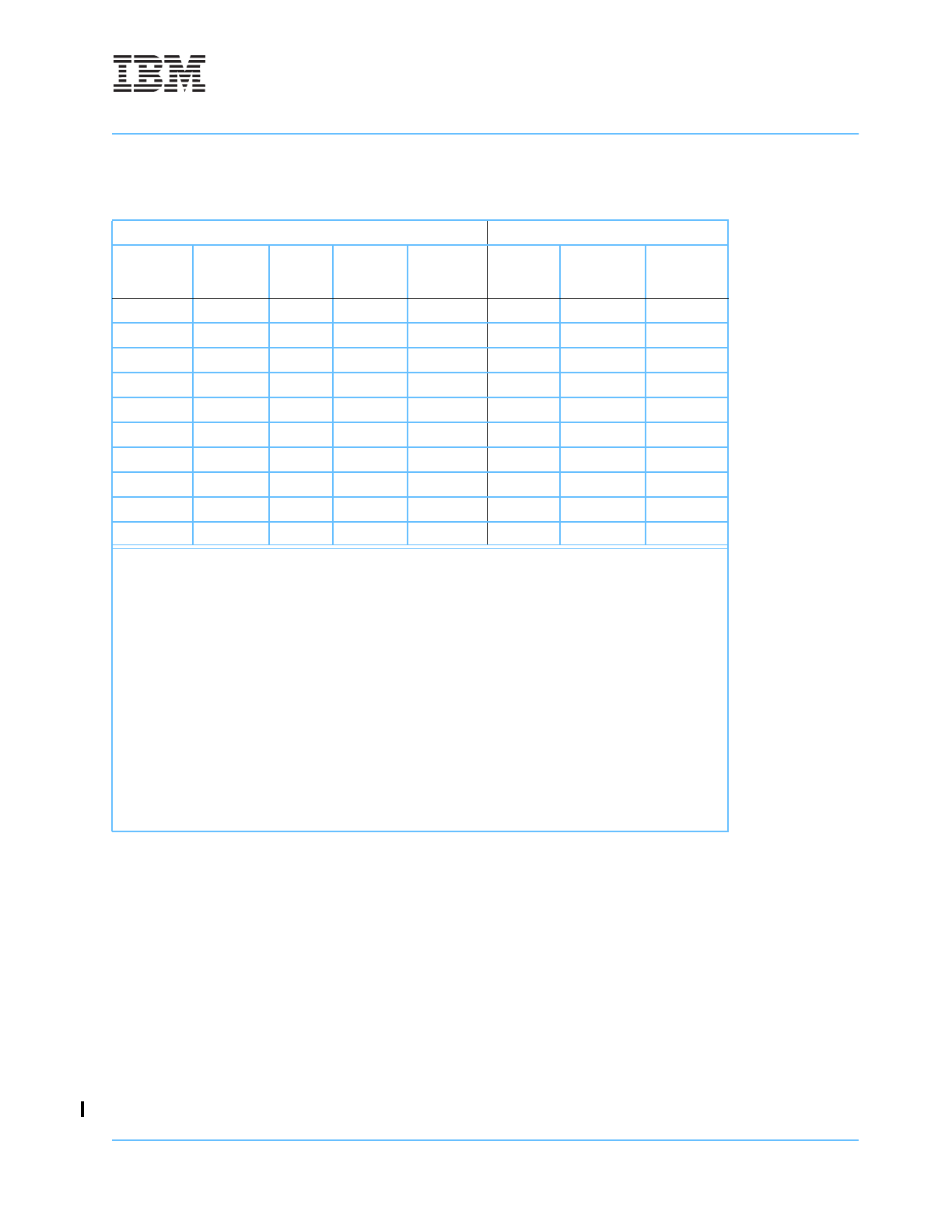

Table 4-5 summarizes how the various storage attributes and other circumstances affect the DCC behavior

on store accesses.

4.3.1.4 Line Flush Operations

When a store operation (or the dcbz instruction) writes data into the data cache without also writing the data

to main memory, the cache line is said to become dirty, meaning that the data in the cache is the current

value, whereas the value in memory is obsolete. Of course, when such a dirty cache line is replaced (due, for

example, to a new cache line fill overwriting the existing line in the cache), the data in the cache line must be

copied to memory. Otherwise, the results of the previous store operation[s] that caused the cache line to be

marked as dirty would be lost. The operation of copying a dirty cache line to memory is referred to as a cache

line flush. Cache lines are flushed either due to being replaced when a new cache line is filled, or in response

to an explicit software flush request associated with the execution of a dcbst or dcbf instruction.

The DCC implements four dirty bits per cache line, one for each aligned doubleword within the cache line.

Whenever any byte of a given doubleword is stored into a data cache line without also writing that same byte

to memory, the corresponding dirty bit for that cache line is set (if CCR1[FFF] is set, then all four dirty bits are

Table 4-5. Data Cache Behavior on Store Accesses

Store Access Attributes DCC Actions

Caching

Inhibited

(I)

Hit/Miss SWOA

Write

through

(W)

Guarded

(G)

Write

Cache?

Write

Memory?

Gather?

1

0 Hit — 0 — Yes No N/A

0 Hit — 1 0 Yes Yes Yes

0 Hit — 1 1 Yes Yes No

0 Miss 0 0 — Yes No N/A

0 Miss 0 1 0 Yes Yes Yes

0 Miss 0 1 1 Yes Yes No

0 Miss 1 — 0 No Yes Yes

0 Miss 1 — 1 No Yes No

1—

2

——

3

0 No Yes Yes

4

1—

2

——

3

1 No Yes No

Note 1: If store gathering is disabled altogether (by setting CCR0[DSTG] to 1), then

such gathering will not occur, regardless of the indication in this table.

Furthermore, where this table indicates that store gathering may occur it is

presumed that the operations being gathered are targeting the same aligned

quadword of memory, and are contiguous with respect to each other.

Note 2: It is a programming error for a data cache hit to occur on a store access to a

caching inhibited page. The result of such an access is undefined.

Note 3: It is programming error for the write-through storage attribute to be set for a

page which also has the caching inhibited storage attribute set. The result of an

access to such a page is undefined.

Note 4: Stores to caching inhibited memory locations may only be gathered with

previous store operations if none of the targeted bytes overlap with the bytes

targeted by the previous store operations.