User’s Manual

Preliminary PPC440x5 CPU Core

instalfa.fm.

September 12, 2002

Page 541 of 589

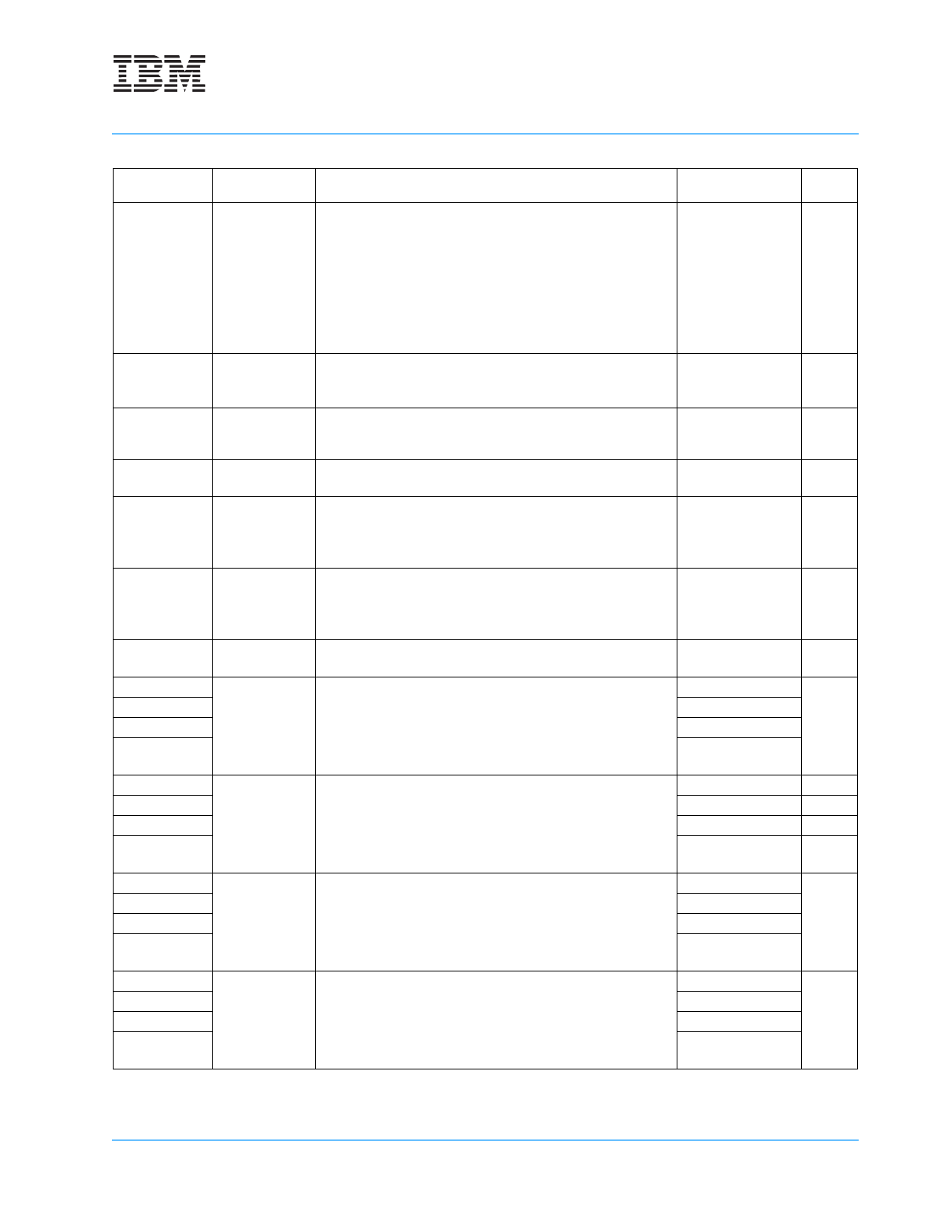

lswx

RT, RA, RB

Load consecutive bytes from EA=(RA|0)+(RB).

Number of bytes n=XER[TBC].

Stack bytes into words in CEIL(n/4)

consecutive registers starting with RT, to

R

FINAL

← ((RT + CEIL(n/4) – 1) % 32).

GPR(0) is consecutive to GPR(31).

RA is not altered unless RA = R

FINAL

.

RB is not altered unless RB = R

FINAL

.

If n=0, content of RT is undefined.

337

lwarx

RT, RA, RB

Load word from EA = (RA|0) + (RB) and place in RT,

(RT) ← MS(EA,4).

Set the Reservation bit.

339

lwbrx

RT, RA, RB

Load word from EA = (RA|0) + (RB) then reverse byte order,

(RT) ← MS(EA+3,1) || MS(EA+2,1) ||

MS(EA+1,1) || MS(EA,1).

340

lwz

RT, D(RA)

Load word from EA = (RA|0) + EXTS(D) and place in RT,

(RT) ← MS(EA,4).

341

lwzu

RT, D(RA)

Load word from EA = (RA|0) + EXTS(D) and place in RT,

(RT) ← MS(EA,4).

Update the base address,

(RA) ← EA.

342

lwzux

RT, RA, RB

Load word from EA = (RA|0) + (RB) and place in RT,

(RT) ← MS(EA,4).

Update the base address,

(RA) ← EA.

343

lwzx

RT, RA, RB

Load word from EA = (RA|0) + (RB) and place in RT,

(RT) ← MS(EA,4).

344

macchw

RT, RA, RB

prod

0:31

← (RA)

16:31

× (RB)

0:15

temp

0:32

← prod

0:31

+ (RT)

(RT) ← temp

1:32

345

macchw. CR[CR0]

macchwo XER[SO, OV]

macchwo.

CR[CR0]

XER[SO, OV]

macchwu

RT, RA, RB

prod

0:31

← (RA)

16:31

× (RB)

0:15

temp

0:32

← prod

0:31

+ (RT)

(RT) ← temp

1:32

348

macchwu. CR[CR0]

macchwuo XER[SO, OV]

macchwuo.

CR[CR0]

XER[SO, OV]

macchws

RT, RA, RB

prod

0:31

← (RA)

16:31

× (RB)

0:15

temp

0:32

← prod

0:31

+ (RT)

if ((prod

0

= RT

0

) ∧ (RT

0

≠ temp

1

)) then

(RT) ← (RT

0

∨

31

(¬RT

0

))

else (RT) ← temp

1:32

346

macchws. CR[CR0]

macchwso XER[SO, OV]

macchwso.

CR[CR0]

XER[SO, OV]

macchwsu

RT, RA, RB

prod

0:31

← (RA)

16:31

× (RB)

0:15

temp

0:32

← prod

0:31

+ (RT)

(RT) ← (temp

1:32

∨

31

temp

0

)

347

macchwsu. CR[CR0]

macchwsuo XER[SO, OV]

macchwsuo.

CR[CR0]

XER[SO, OV]

Table A-1. PPC440x5 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed

Page