User’s Manual

PPC440x5 CPU Core Preliminary

Page 88 of 589

init.fm.

September 12, 2002

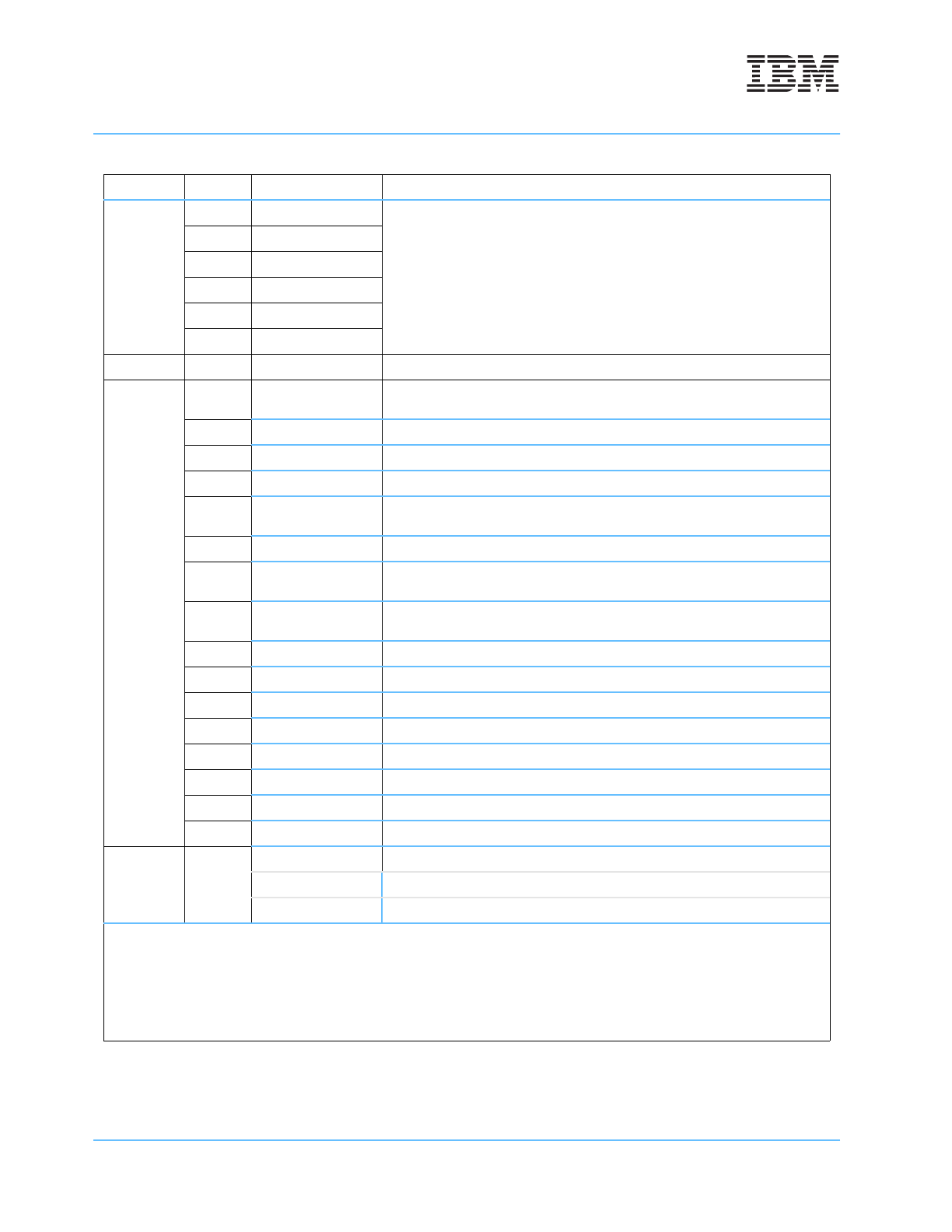

RSTCFG

U0 System-dependent

All RSTCFG fields are specified by core input signals

U1 System-dependent

U2 System-dependent

U3 System-dependent

E System-dependent

EPRN System-dependent

TCR WRC 0b00 Watchdog Timer reset disabled

TLBentry

1

EPN

0:19

0xFFFFF

Match EA of initial reset instruction (EPN

20:21

are undefined, as they are not

compared to the EA because the page size is 4KB).

V 1 Translation table entry for the initial program memory page is valid.

TS 0 Initial program memory page is in system-level virtual address space.

SIZE 0b0001 Initial program memory page size is 4KB.

TID 0x00

Initial program memory page is globally shared; no match required against PID

register.

RPN

0:21

0xFFFFF || 0b00 Initial program memory page mapped effective=real.

ERPN System-dependent

Extended real page number of the initial program memory page is specified by

core input signals.

U0–U3 System-dependent

Reset value of user-definable storage attributes are specified by core input sig-

nals

W 0 Write-through storage attribute disabled.

I 1 Caching inhibited storage attribute enabled.

M 0 Memory coherent storage attribute disabled.

G 1 Guarded storage attribute enabled.

E System-dependent Reset value of endian storage attribute is specified by a core input signal.

SX 1 Supervisor mode execution access enabled.

SW 0 Supervisor mode write access disabled.

SR 1 Supervisor mode read access enabled.

TSR WRS

Copy of TCR[WRC] If reset caused by Watchdog Timer

Unchanged If reset not caused by Watchdog Timer

Undefined After power-up

Note 1: “TLBentry” refers to an entry in the shadow instruction and data TLB arrays that is automatically

configured by the PPC440x5 core to enable fetching and reading (but not writing) from the initial

program memory page. This entry is not architecturally visible to software, and is invalidated upon any

context synchronizing operation. Software must initialize a corresponding entry in the main unified

TLB array before executing any operation which could lead to a context synchronization. See

Initialization Software Requirements on page 89 for more information.

Table 3-1. Reset Values of Registers and Other PPC440x5 Facilities

Resource Field Reset Value Comment