User’s Manual

Preliminary PPC440x5 CPU Core

mmu.fm.

September 12, 2002

Page 135 of 589

Maintenance of TLB entries is under software control. System software determines the TLB entry replace-

ment strategy and the format and use of any page table information. A TLB entry contains all of the informa-

tion required to identify the page, to specify the address translation, to control the access permissions, and to

designate the storage attributes.

A TLB entry is written by copying information from a GPR and the MMUCR[STID] field, using a series of three

tlbwe instructions. A TLB entry is read by copying the information into a GPR and the MMUCR[STID] field,

using a series of three tlbre instructions. Software can also search for specific TLB entries using the tlbsx[.]

instruction. See TLB Management Instructions on page 152 for more information on these instructions.

Each TLB entry identifies a page and defines its translation, access controls, and storage attributes. Accord-

ingly, fields in the TLB entry fall into four categories:

• Page identification fields (information required to identify the page to the hardware translation mecha-

nism).

• Address translation fields

• Access control fields

• Storage attribute fields

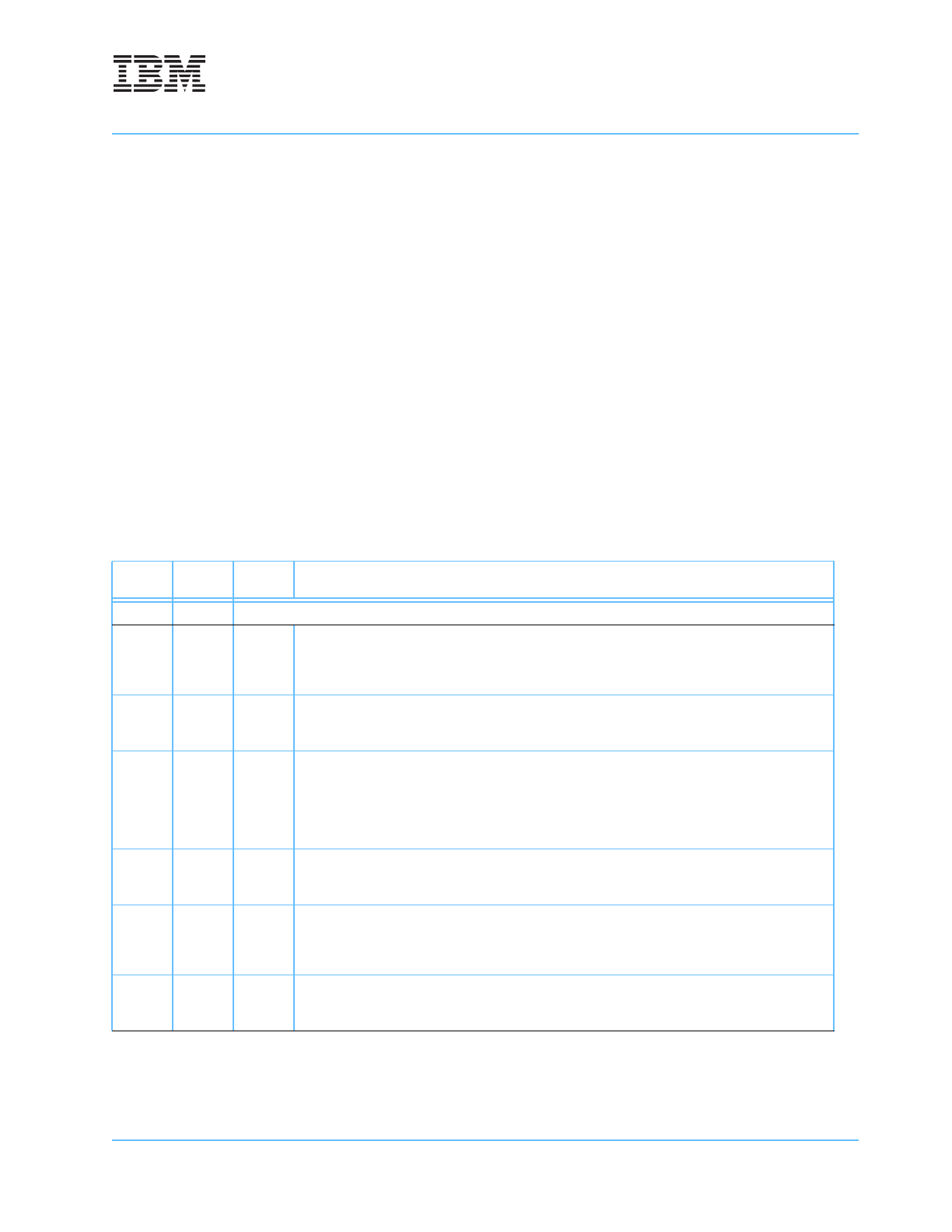

Table 5-1 summarizes the TLB entry fields for each of the categories.

Table 5-1. TLB Entry Fields

TLB

Word

Bit Field Description

Page Identification Fields

0 0:21 EPN

Effective Page Number (variable size, from 4 - 22 bits)

Bits 0:n–1 of the EPN field are compared to bits 0:n–1 of the effective address (EA) of the storage

access (where n = 32–log

2

(page size in bytes) and page size is specified by the SIZE field of the

TLB entry). See Table 5-2 on page 140.

022V

Valid (1 bit)

This bit indicates that this TLB entry is valid and may be used for translation. The Valid bit for a

given entry can be set or cleared with a tlbwe instruction.

023TS

Translation Address Space (1 bit)

This bit indicates the address space this TLB entry is associated with. For instruction fetch

accesses, MSR[IS] must match the value of TS in the TLB entry for that TLB entry to provide the

translation. Likewise, for data storage accesses (including instruction cache management opera-

tions), MSR[DS] must match the value of TS in the TLB entry. For the tlbsx[.] instruction, the

MMUCR[STS] field must match the value of TS.

0 24:27 SIZE

Page Size (4 bits)

The SIZE field specifies the size of the page associated with the TLB entry as 4

SIZE

KB, where

SIZE ∈ {0, 1, 2, 3, 4, 5, 7, 9}. See Table 5-2 on page 140.

0 28:31 TPAR

Tag Parity (4 bits)

The TPAR field reads the parity bits associated with TLB word 0. These bits will be loaded into a

GPR as a result of a tlbre, but are ignored when executing a tlbwe, since the parity to be writ-

ten is calculated by the processor hardware.

0 32:39 TID

Translation ID (8 bits)

Field used to identify a globally shared page (TID=0) or the process ID of the owner of a private

page (TID<>0). See Page Identification on page 138.