User’s Manual

PPC440x5 CPU Core Preliminary

Page 86 of 589

init.fm.

September 12, 2002

nizing operation (including causing any exceptions which would lead to an interrupt), since a context

synchronizing operation will invalidate the shadow TLB entries.

Initialization software should consider all other resources within the PPC440x5 core to be undefined after

reset, in order for the initialization sequence to be compatible with other PowerPC implementations. There

are, however, additional core resources which are initialized by reset, in order to guarantee correct and deter-

ministic operation of the processor during the initialization sequence. Table 3-1 shows the reset state of all

PPC440x5 core resources which are defined to be initialized by reset. While certain other register fields and

other facilities within the PPC440x5 core may be affected by reset, this is not an architectural nor hardware

requirement, and software must treat those resources as undefined. Likewise, even those resources which

are included in Table 3-1 but which are not identified in the previous list as being architecturally required,

should be treated as undefined by the initialization software.

During chip initialization, some chip control registers must be initialized to ensure proper chip operation.

Peripheral devices can also be initialized as appropriate for the system design.

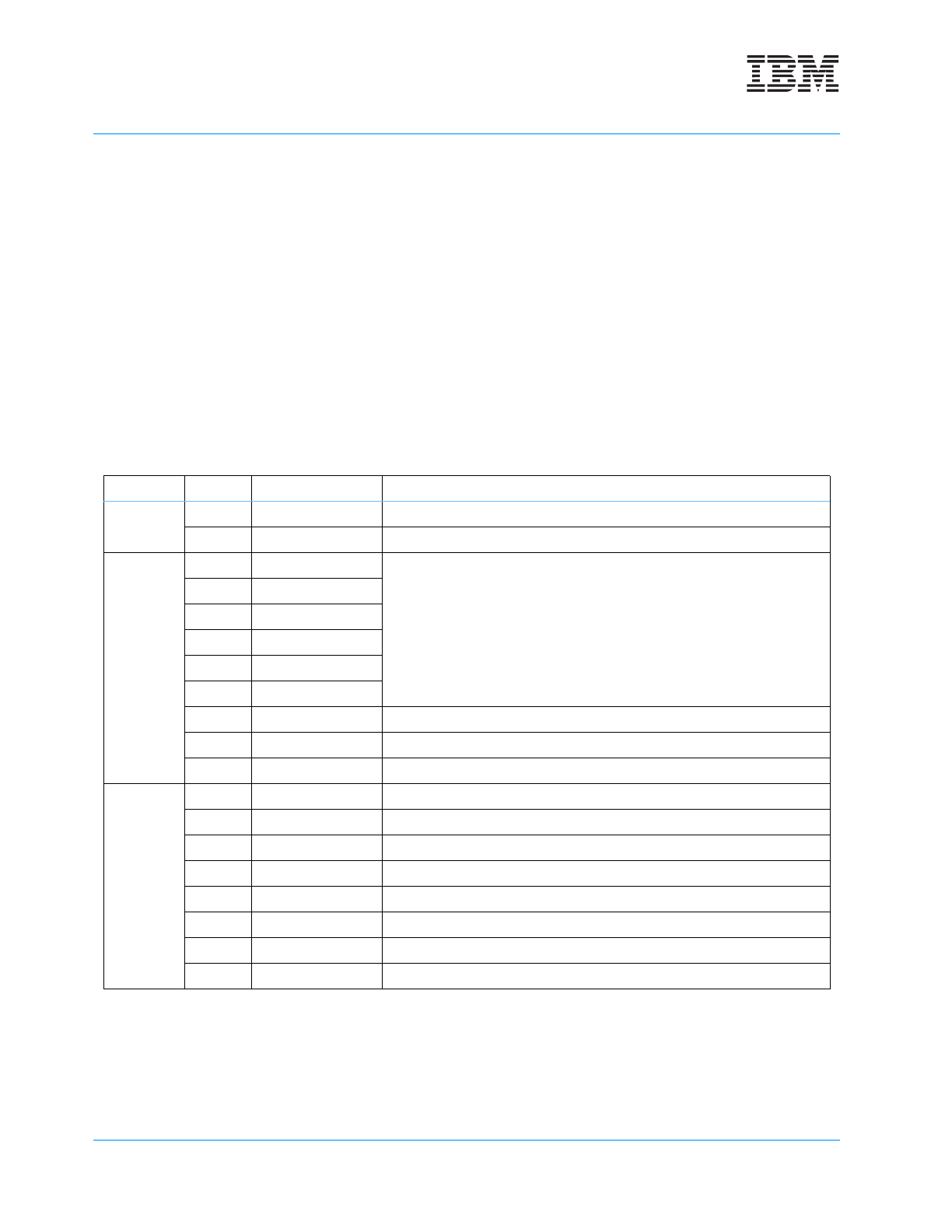

Table 3-1. Reset Values of Registers and Other PPC440x5 Facilities

Resource Field Reset Value Comment

CCR0

DAPUIB 0 Enable broadcast of instruction data to auxiliary processor interface

DTB 0 Enable broadcast of trace information

CCR1

ICDPEI 0

Disable Parity Error Insertion (enabled only for s/w testing)

ICTPEI 0

DCTPEI 0

DCDPEI 0

DCUPEI 0

DCMPEI 0

FCOM 0 Do not force cache ops to miss.

MMUPEI 0 Disable Parity Error Insertion (enabled only for s/w testing)

FFF 0 Flush only as much data from dirty lines as needed.

DBCR0

EDM 0 External Debug mode disabled

RST 0b00 Software-initiated debug reset disabled

ICMP 0 Instruction completion debug events disabled

BRT 0 Branch taken debug events disabled

IAC1 0 Instruction Address Compare 1 (IAC1) debug events disabled

IAC2 0 IAC2 debug events disabled

IAC3 0 IAC3 debug events disabled

IAC4 0 IAC4 debug events disabled