User’s Manual

Preliminary PPC440x5 CPU Core

debug.fm.

September 12, 2002

Page 237 of 589

8.3.9 Unconditional Debug Event (UDE)

UDE debug events occur when a debug tool asserts the unconditional debug event request via the JTAG

interface. The UDE debug event is the only event which does not have a corresponding enable field in

DBCR0.

When operating in external debug mode or debug wait mode, the occurrence of a UDE debug event is

recorded in DBSR[UDE] and causes the processor to enter the stop state and cease processing instructions.

The program counter will contain the address of the instruction which would have executed next, had the

UDE debug event not occurred. Similarly, when operating in internal debug mode with Debug interrupts

enabled (MSR[DE] = 1), the occurrence of a UDE debug event is recorded in DBSR[UDE] and a Debug inter-

rupt will occur with CSRR0 set to the address of the instruction which would have executed next, had the

UDE debug event not occurred.

When operating in internal debug mode (and not also in external debug mode nor debug wait mode) with

Debug interrupts disabled (MSR[DE] = 0), the occurrence of a UDE debug event will set DBSR[UDE], along

with the Imprecise Debug Event (IDE) field of the DBSR. The Debug interrupt will not occur immediately.

Instead, instruction execution continues, and a Debug interrupt will occur if and when MSR[DE] is set to 1,

thereby enabling Debug interrupts, assuming software has not cleared the UDE debug event status from the

DBSR in the meantime. Upon such a “delayed” interrupt, the Debug interrupt handler software may query the

DBSR[IDE] field to determine that the Debug interrupt has occurred imprecisely.

When operating in trace mode, the occurrence of a UDE debug event simply sets DBSR[UDE] and is indi-

cated over the trace interface, and instruction execution continues.

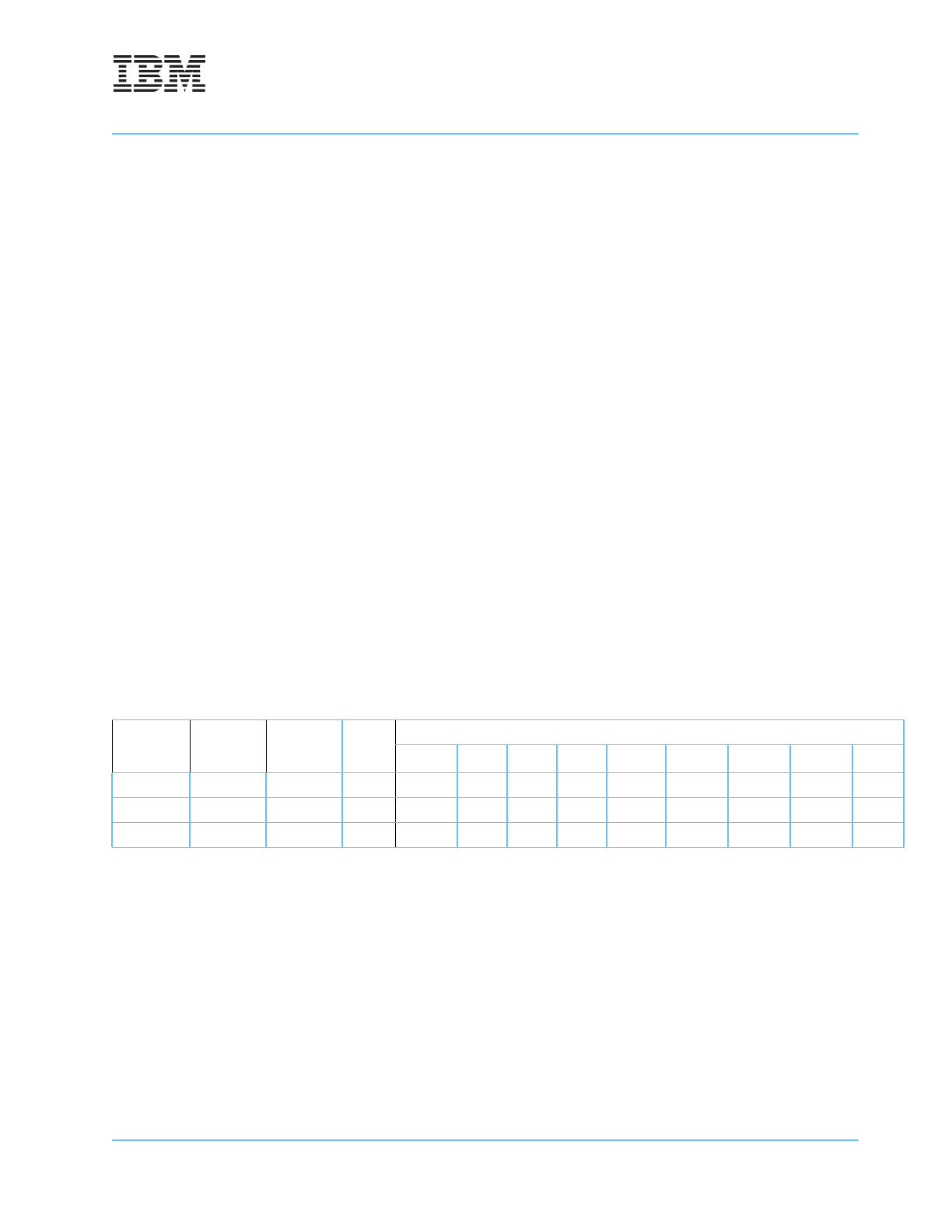

8.3.10 Debug Event Summary

Table 8-3 summarizes each of the debug event types, and the effect of debug mode and MSR[DE] on their

occurrence.

Table 8-3. Debug Event Summary

External

Debug

Mode

Debug

Wait

Mode

Internal

Debug

Mode

MSR

DE

Debug Events

IAC DAC DVC BRT TRAP RET ICMP IRPT UDE

Enabled — — — Yes Yes Yes Yes Yes Yes Yes Yes Yes

— Enabled — — Yes Yes Yes Yes Yes Yes Yes Yes Yes

Disabled Disabled Enabled 1 Yes Yes Yes Yes Yes Yes Yes Note 1 Yes