User’s Manual

Preliminary PPC440x5 CPU Core

cache.fm.

September 12, 2002

Page 113 of 589

mficdbdr regC # move instruction information into GPR C

mficdbtrh regD # move high portion of tag into GPR D

mficdbtrl regE # move low portion of tag into GPR E

The following figures illustrate the ICDBDR, ICDBTRH, and ICDBTRL.

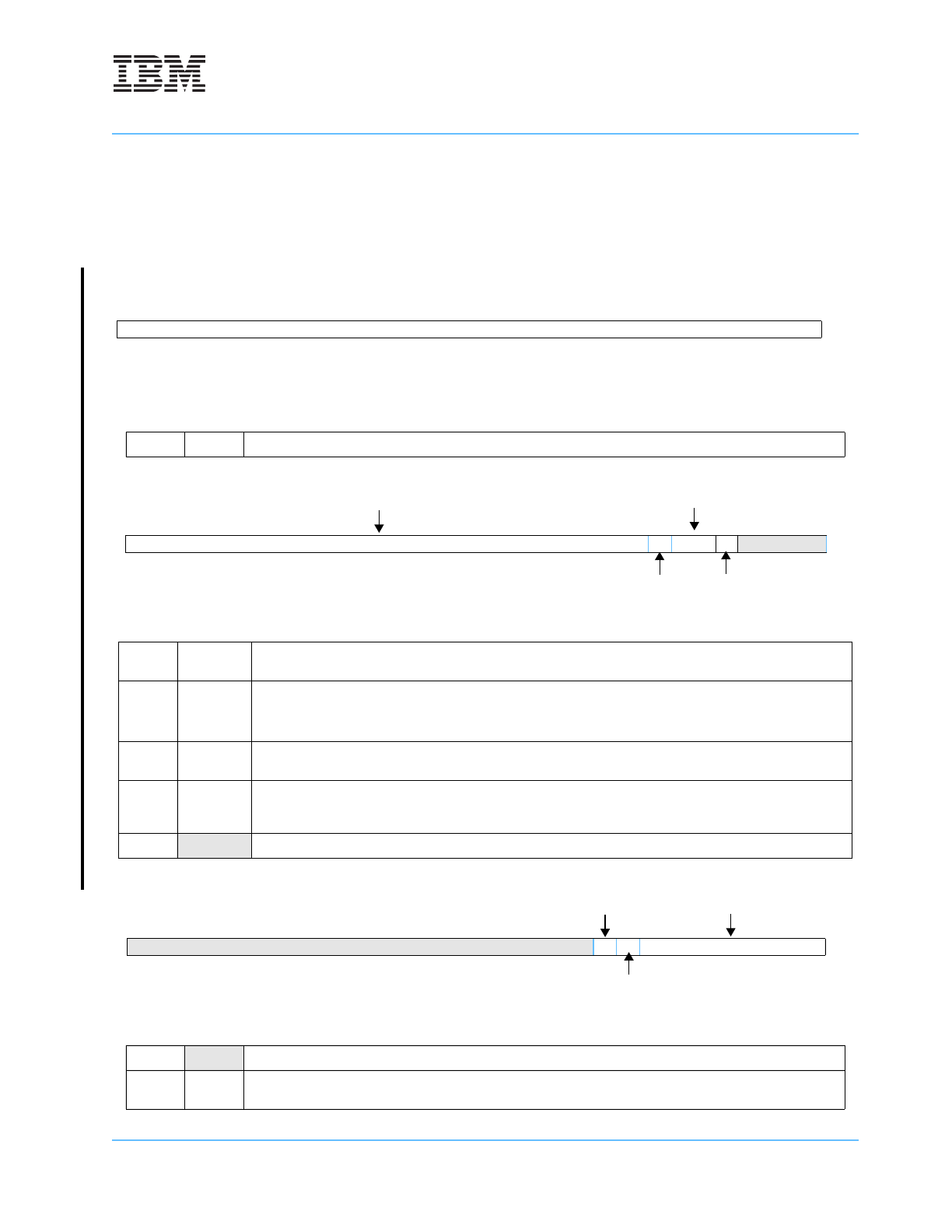

Figure 4-7. Instruction Cache Debug Data Register (ICDBDR)

0:31 Instruction machine code from instruction cache

Figure 4-8. Instruction Cache Debug Tag Register High (ICDBTRH)

0:23 Tag Effective Address

Bits 0:23 of the 32-bit effective address associated

with the cache line read by icread.

24 V

Cache Line Valid

0 Cache line is not valid.

1 Cache line is valid.

The valid indicator for the cache line read by

icread.

25:26 TPAR Tag Parity

The parity bits for the address tag for the cache

line read by icread, if CCR0[CRPE] is set.

27 DAPAR Instruction Data parity

The parity bit for the instruction word at the 32-bit

effective address specified in the icread instruc-

tion, if CCR0[CRPE] is set.

28:31 Reserved

Figure 4-9. Instruction Cache Debug Tag Register Low (ICDBTRL)

0:21 Reserved

22 TS Translation Space

The address space portion of the virtual address

associated with the cache line read by icread.

0 31

0 23 24 25 26 27 28 31

TEA

V

TPAR

DAPAR

0 21 22 23 24 31

TS

TD

TID