PPC440x5 CPU Core User’s Manual Preliminary

Page 250 of 589

instrset.fm.

September 12, 2002

9.1 Instruction Set Portability

To support embedded real-time applications, the PPC440x5 core implements the defined instruction set of

the Book-E Enhanced PowerPC Architecture, with the exception of those operations which are defined for

64-bit implementations only, and those which are defined as floating-point operations. Support for the

floating-point operations is provided via the auxiliary processor interface, while the 64-bit operations are not

supported at all. See Instruction Classes on page 53 for more information on the support for defined instruc-

tions within the PPC440x5.

The PPC440x5 core also implements a number of instructions that are not part of PowerPC Book-E architec-

ture, but are included as part of the PPC440x5. Architecturally, they are considered allocated instructions, as

they use opcodes which are within the allocated class of instructions, which the PowerPC Book-E architec-

ture identifies as being available for implementation-dependent and/or application-specific purposes.

However, all of the allocated instructions which are implemented within the PPC440x5 core are “standard” for

IBM PowerPC 400 Series family of embedded controllers, and are not unique to the PPC440x5.

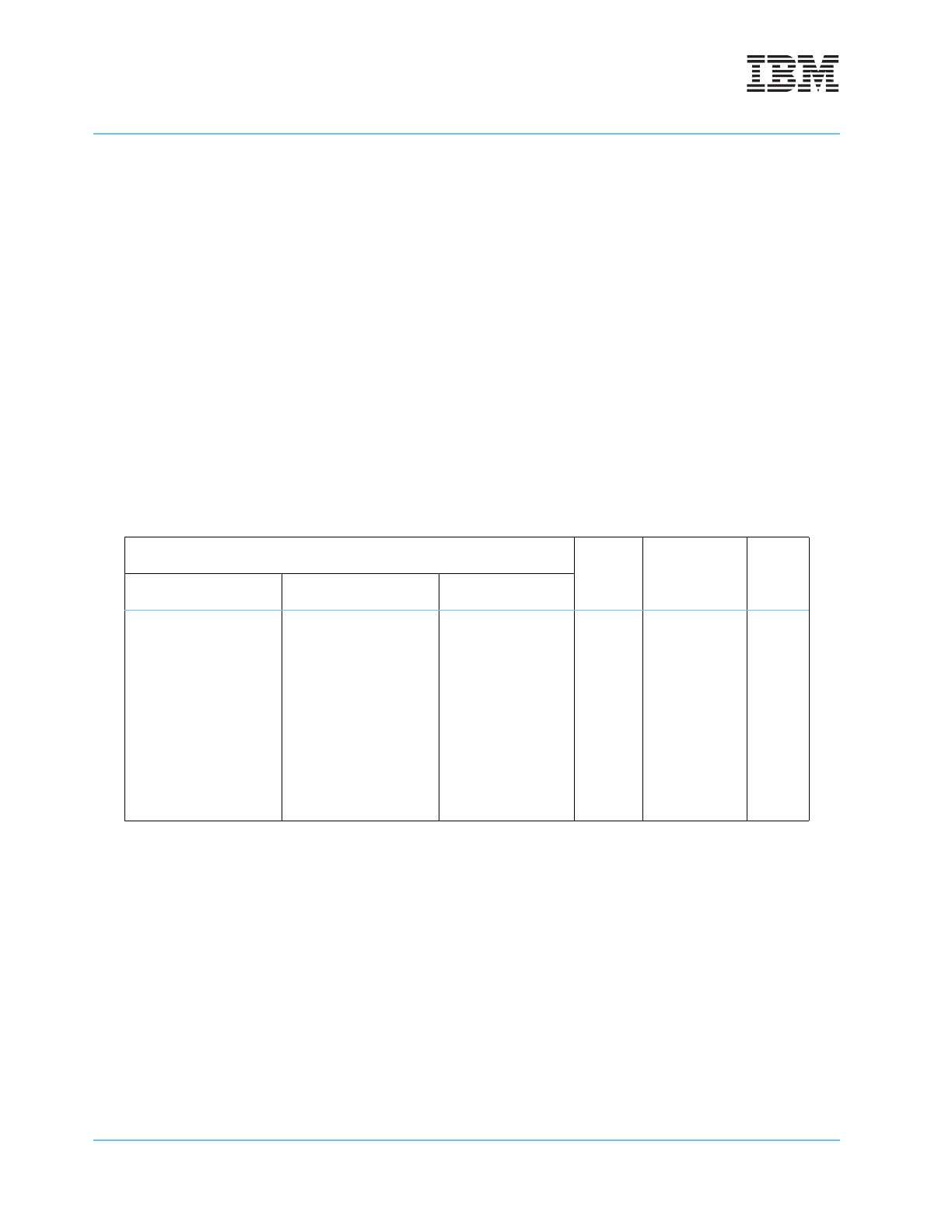

The allocated instructions implemented within the PPC440x5 are divided into four sub-categories, and are

shown in Table 9-2. Programs using these instructions may not be portable to other PowerPC Book-E imple-

mentations.

9.2 Instruction Formats

For more detailed information about instruction formats, including a summary of instruction field usage and

instruction format diagrams for the PPC440x5 core, see Instruction Formats on page 519.

Instructions are four bytes long. Instruction addresses are always word-aligned.

Instruction bits 0 through 5 always contain the primary opcode. Many instructions have an extended opcode

field as well. The remaining instruction bits contain additional fields. All instruction fields belong to one of the

following categories:

• Defined

Table 9-2. Allocated Instructions

Arithmetic Logical

Cache

Management

Cache

Debug

Multiply-Accumulate

Negative

Multiply-Accumulate

Multiply Halfword

macchw[o][.]

macchws[o][.]

macchwsu[o][.]

macchwu[o][.]

machhw[o][.]

machhws[o][.]

machhwsu[o][.]

machhwu[o][.]

maclhw[o][.]

maclhws[o][.]

maclhwsu[o][.]

maclhwu[o][.]

nmacchw[o][.]

nmacchws[o][.]

nmachhw[o][.]

nmachhws[o][.]

nmaclhw[o][.]

nmaclhws[o][.]

mulchw[.]

mulchwu[.]

mulhhw[.]

mulhhwu[.]

mullhw[.]

mullhwu[.]

dlmzb[.]

dccci

iccci

dcread

icread