User’s Manual

PPC440x5 CPU Core Preliminary

Page 142 of 589

mmu.fm.

September 12, 2002

5.5 Access Control

Once a matching TLB entry has been identified and the address has been translated, the access control

mechanism determines whether the program has execute, read, and/or write access to the page referenced

by the address, as described in the following sections.

5.5.1 Execute Access

The UX or SX bit of a TLB entry controls execute access to a page of storage, depending on the operating

mode (user or supervisor) of the processor.

• User mode (MSR[PR] = 1)

Instructions may be fetched and executed from a page in storage while in supervisor mode if the SX access

control bit for that page is equal to 1. If the SX access control bit is equal to 0, then instructions from that page

will not be fetched, and will not be placed into any cache as the result of a fetch request to that page while in

supervisor mode.

Furthermore, if the sequential execution model calls for the execution in supervisor mode of an instruction

from a page that is not enabled for execution in supervisor mode (that is, SX=0 when MSR[PR]=0), an

Execute Access Control exception type Instruction Storage interrupt is taken (See Interrupts and Exceptions

on page 159 for more information).

5.5.2 Write Access

The UW or SW bit of aTLB entry controls write access to a page, depending on the operating mode (user or

supervisor) of the processor.

• User mode (MSR[PR] = 1)

Store operations (including the store-class cache management instruction dcbz) are permitted to a page

in storage while in user mode if the UW access control bit for that page is equal to 1. If execution of a

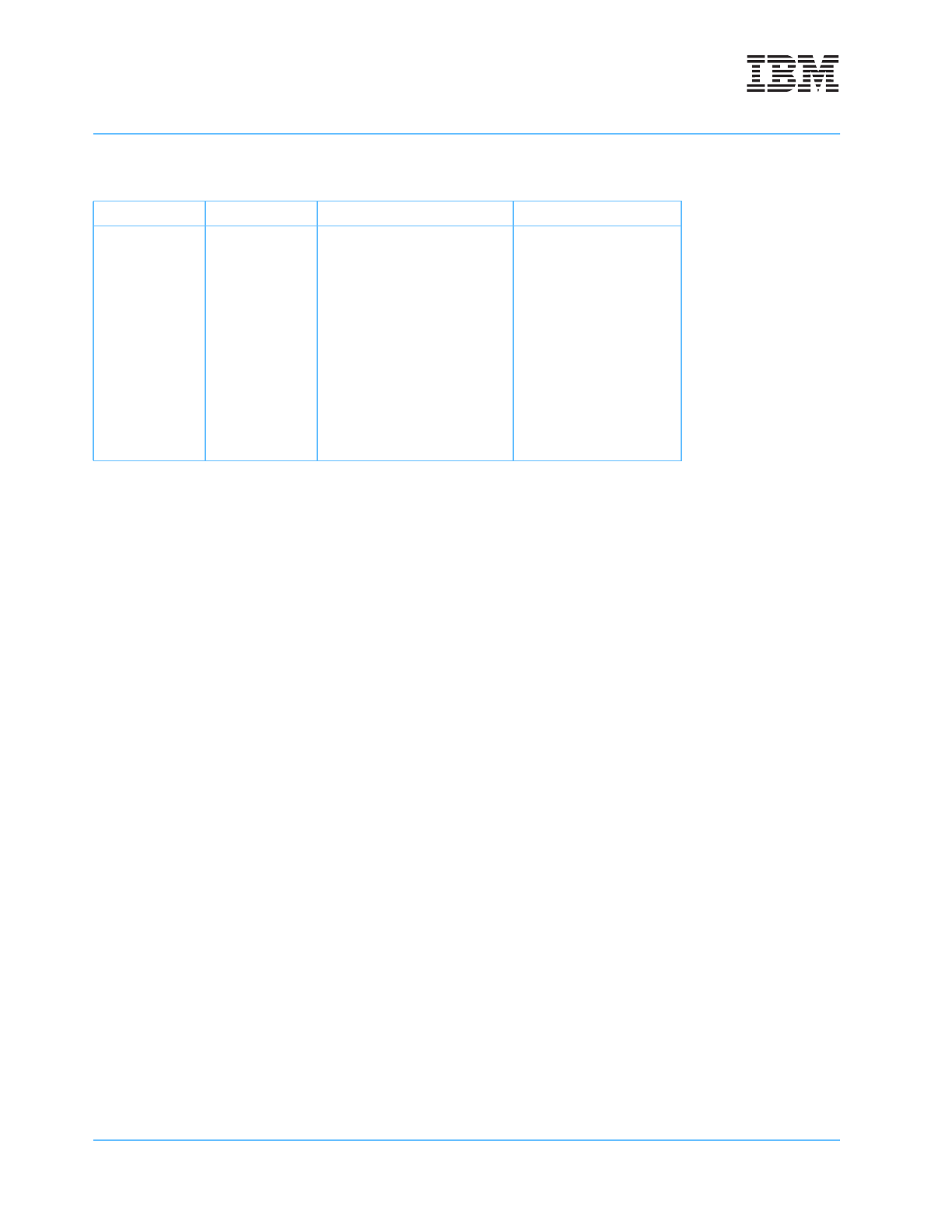

Table 5-3. Page Size and Real Address Formation

SIZE Page Size RPN bits required to be 0 Real Address

0b0000

0b0001

0b0010

0b0011

0b0100

0b0101

0b0110

0b0111

0b1000

0b1001

0b1010

0b1011

0b1100

0b1101

0b1110

0b1111

1KB

4KB

16KB

64KB

256KB

1MB

not supported

16MB

not supported

256MB

not supported

not supported

not supported

not supported

not supported

not supported

none

RPN

20:21

=0

RPN

18:21

=0

RPN

16:21

=0

RPN

14:21

=0

RPN

12:21

=0

not supported

RPN

8:21

=0

not supported

RPN

4:21

=0

not supported

not supported

not supported

not supported

not supported

not supported

RPN

0:21

|| EA

22:31

RPN

0:19

|| EA

20:31

RPN

0:17

|| EA

18:31

RPN

0:15

|| EA

16:31

RPN

0:13

|| EA

14:31

RPN

0:11

|| EA

12:31

not supported

RPN

0:7

|| EA

8:31

not supported

RPN

0:3

|| EA

4:31

not supported

not supported

not supported

not supported

not supported

not supported