User’s Manual

PPC440x5 CPU Core Preliminary

Page 72 of 589

prgmodel.fm.

September 12, 2002

2.6.2 Integer Exception Register (XER)

The XER records overflow and carry indications from integer arithmetic and shift instructions. It also provides

a byte count for string indexed integer storage access instructions (lswx and stswx). Note that the term

exception in the name of this register does not refer to exceptions as they relate to interrupts, but rather to the

arithmetic exceptions of carry and overflow.

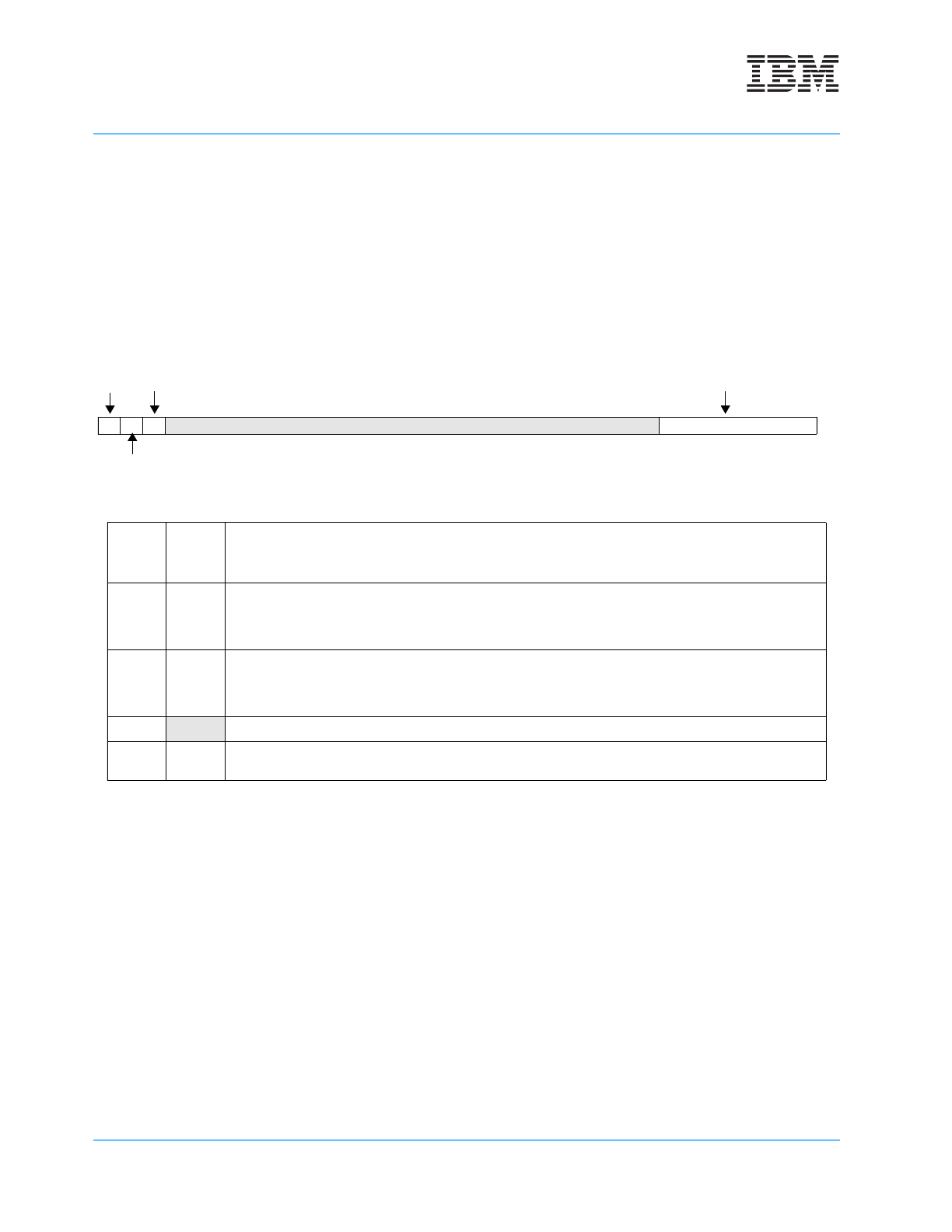

Figure 2-7 illustrates the fields of the XER, while Tables 2-25 and 2-26 list the instructions which update

XER[SO,OV] and the XER[CA] fields, respectively. The sections which follow the figure and tables describe

the fields of the XER in more detail.

Access to the XER is non-privileged.

Figure 2-7. Integer Exception Register (XER)

0SO

Summary Overflow

0 No overflow has occurred.

1 Overflow has occurred.

Can be set by mtspr or by integer or auxiliary

processor instructions with the [o] option; can be

reset by mtspr or by mcrxr.

1OV

Overflow

0 No overflow has occurred.

1 Overflow has occurred.

Can be set by mtspr or by integer or allocated

instructions with the [o] option; can be reset by

mtspr, by mcrxr, or by integer or allocated

instructions with the [o] option.

2CA

Carry

0 Carry has not occurred.

1 Carry has occurred.

Can be set by mtspr or by certain integer arith-

metic and shift instructions; can be reset by

mtspr,bymcrxr, or by certain integer arithmetic

and shift instructions.

3:24 Reserved

25:31 TBC Transfer Byte Count

Used as a byte count by lswx and stswx; written

by dlmzb[.] and by mtspr.

0123 24 25 31

SO

OV

CA

TBC