User’s Manual

Preliminary PPC440x5 CPU Core

timers.fm.

September 12, 2002

Page 217 of 589

7.7 Freezing the Timer Facilities

The debug mechanism provides a means for temporarily “freezing” the timers upon a debug exception.

Specifically, the time base and Decrementer can be prevented from incrementing and decrementing, respec-

tively, whenever a debug exception is recorded in the Debug Status Register (DBSR). This allows a

debugger to simulate the appearance of “real time”, even though the application has been temporarily

“halted” to service the debug event.

See Chapter 8, “Debug Facilities” for more information on freezing the timers.

7.8 Selection of the Timer Clock Source

The source clock of the timers is selected by the Timer Clock Select (TCS) field of the Core Configuration

Register 1 (CCR1). When set to zero, CCR1[TCS] selects the CPU clock. This is the highest frequency timer

clock source.

When set to one, CCR1[TCS] selects an input to the CPU core as the timer clock. The input is sampled by a

latch clocked by the CPU clock, and so cannot cycle any faster than 1/2 the frequency of the CPU clock.

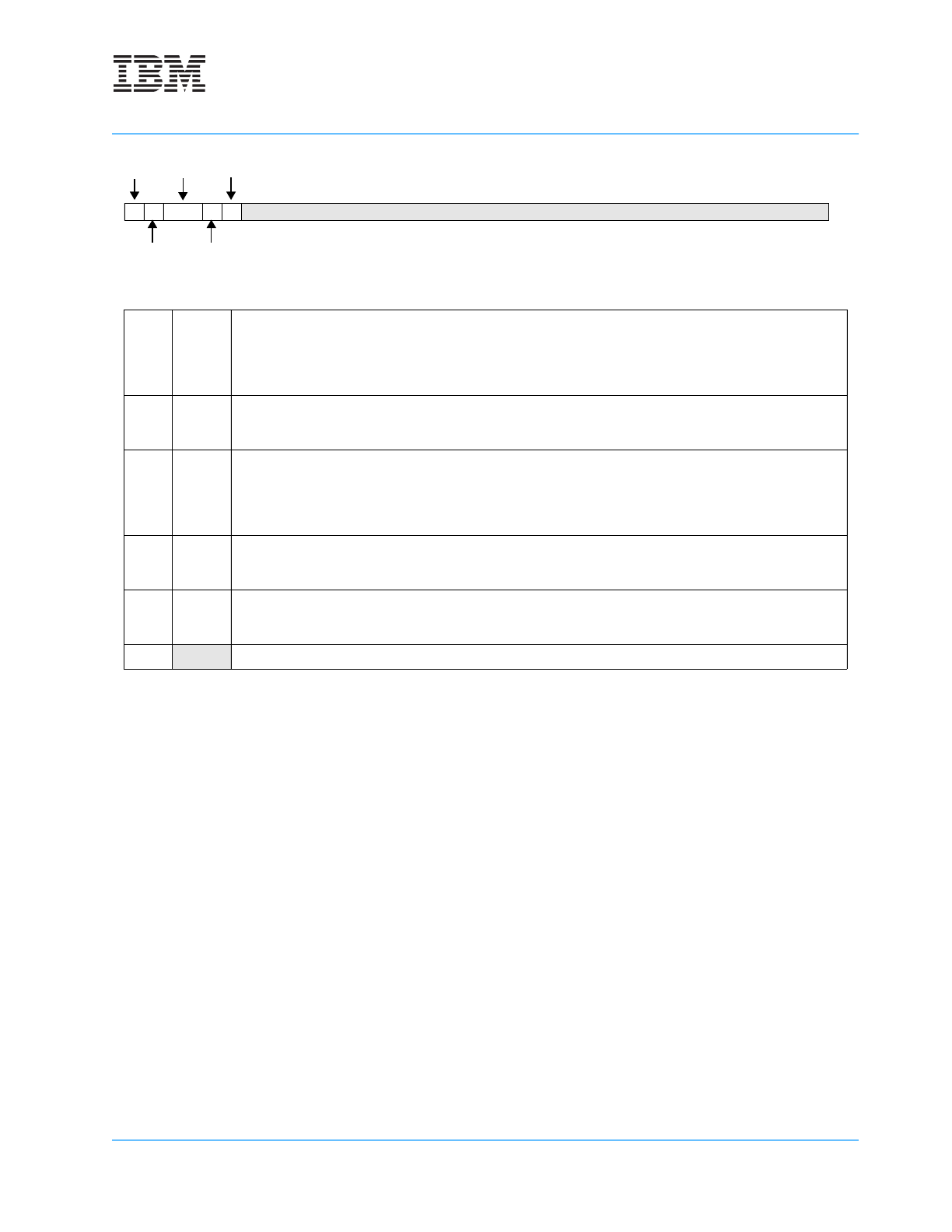

Figure 7-8. Timer Status Register (TSR)

0 ENW

Enable Next Watchdog Timer Exception

0 Action on next Watchdog Timer exception is to set

TSR[ENW] = 1.

1 Action on next Watchdog Timer exception is governed

by TSR[WIS].

1 WIS

Watchdog Timer Interrupt Status

0 Watchdog Timer exception has not occurred.

1 Watchdog Timer exception has occurred.

2:3 WRS

Watchdog Timer Reset Status

00 No Watchdog Timer reset has occurred.

01 Core reset was forced by Watchdog Timer.

10 Chip reset was forced by Watchdog Timer.

11 System reset was forced by Watchdog Timer.

4 DIS

Decrementer Interrupt Status

0 Decrementer exception has not occurred.

1 Decrementer exception has occurred.

5 FIS

Fixed Interval Timer (FIT) Interrupt Status

0 Fixed Interval Timer exception has not occurred.

1 Fixed Interval Timer exception has occurred.

6:31 Reserved

0123456 31

ENW

WIS

WRS FIS

DIS