MMUCR

Memory Management Control Register

Preliminary PPC440x5 CPU Core User’s Manual

regsumm440core.fm.

September 12, 2002 Page 503 of 589

MMUCR

SPR 0x3B2 Supervisor R/W

See Memory Management Unit Control Register (MMUCR) on page 148.

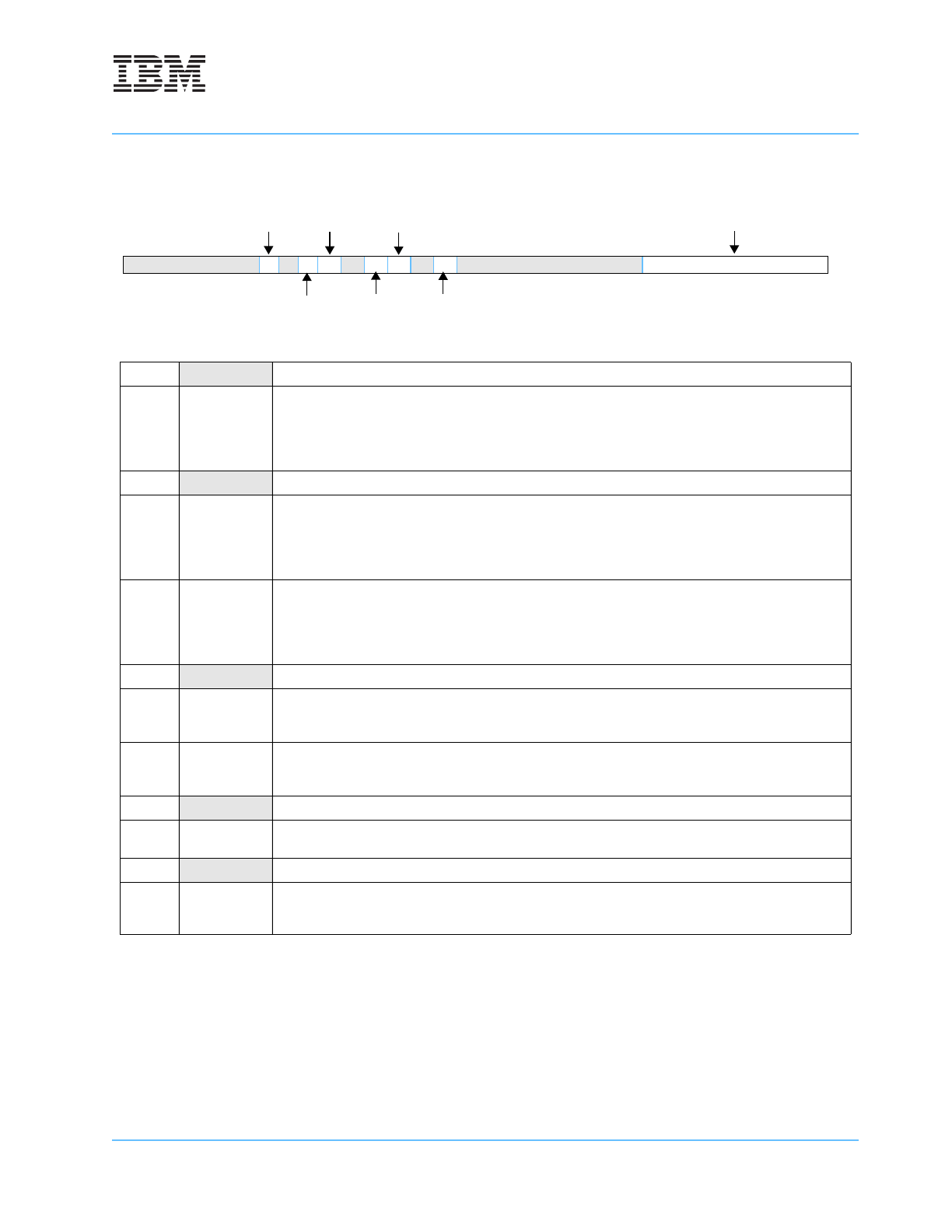

Figure 10-36. Memory Management Unit Control Register (MMUCR)

0:6 Reserved

7 SWOA

Store Without Allocate

0 Cacheable store misses allocate a line in the

data cache.

1 Cacheable store misses do not allocate a line

in the data cache.

If MMUCR[U2SWOAE] = 1, this field is ignored.

8 Reserved

9 U1TE

U1 Transient Enable

0 Disable U1 storage attribute as transient

storage attribute.

1 Enable U1 storage attribute as transient

storage attribute.

10 U2SWOAE

U2 Store without Allocate Enable

0 Disable U2 storage attribute control of store

without allocate.

1 Enable U2 storage attribute control of store

without allocate.

If MMUCR[U2SWOAE] = 1, the U2 storage

attribute overrides MMUCR[SWOA].

11 Reserved

12 DULXE

Data Cache Unlock Exception Enable

0 Data cache unlock exception is disabled.

1 Data cache unlock exception is enabled.

dcbf in user mode causes a Cache Locking

exception type Data Storage interrupt when

MMUCR[DULXE] is 1.

13 IULXE

Instruction Cache Unlock Exception Enable

0 Instruction cache unlock exception is disabled.

1 Instruction cache unlock exception is enabled.

icbi in user mode causes a Cache Locking

exception type Data Storage interrupt when

MMUCR[IULXE] is 1.

14 Reserved

15 STS Search Translation Space

Specifies the value of the translation space (TS)

field for tlbsx[.]

16:23 Reserved

24:31 STID Search Translation ID

Specifies the value of the TID field for the

tlbsx[.]; also used to transfer a TLB entry’s TID

value for tlbre and tlbwe .

0 67891011 12 13 14 15 16 23 24 31

SWOA

U1TE

U2SWOAE

DULXE

IULXE

STS

STID