User’s Manual

PPC440x5 CPU Core Preliminary

Page 166 of 589

intrupts.fm.

September 12, 2002

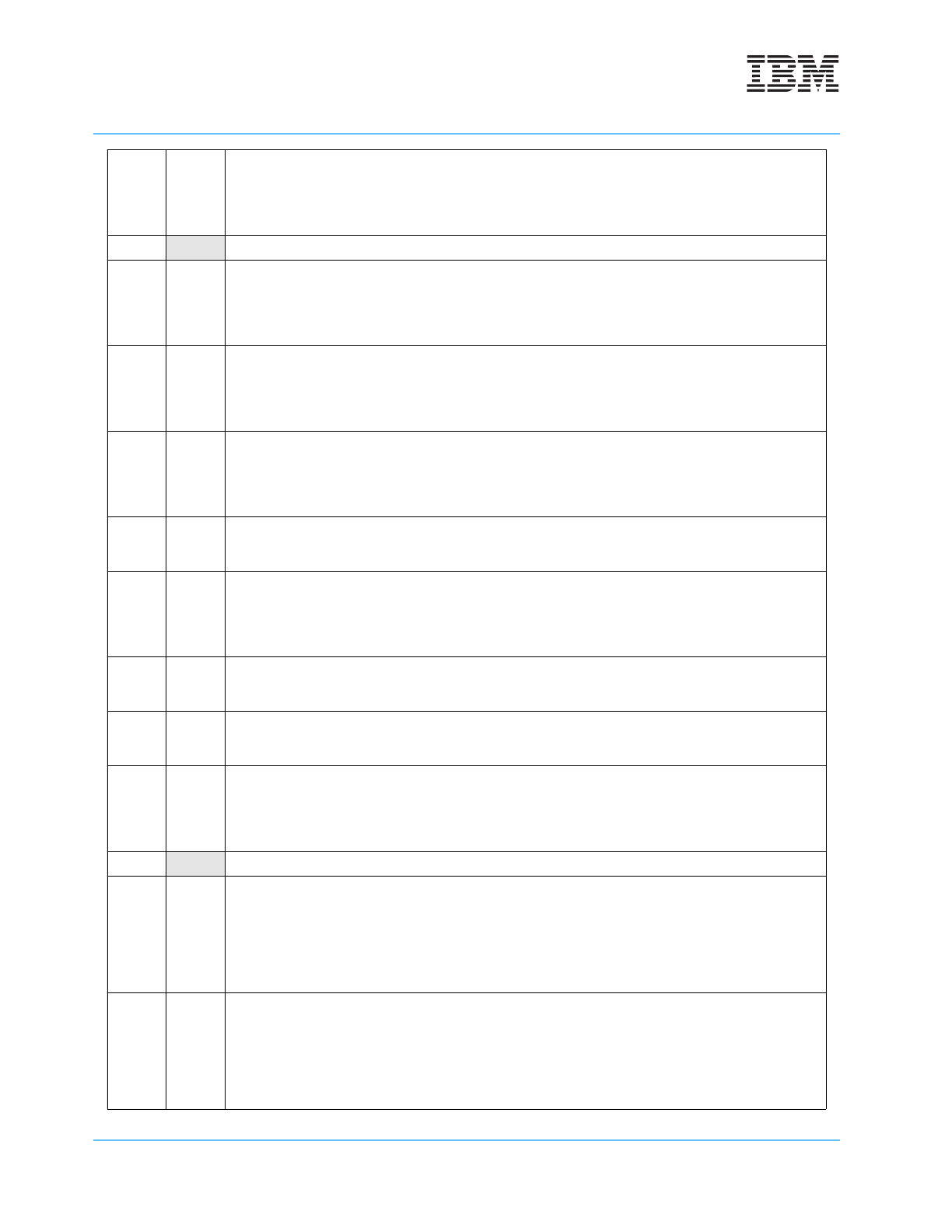

14 CE

Critical Interrupt Enable

0 Critical Input and Watchdog Timer interrupts are

disabled.

1 Critical Input and Watchdog Timer interrupts are

enabled.

15 Reserved

16 EE

External Interrupt Enable

0 External Input, Decrementer, and Fixed Interval

Timer interrupts are disabled.

1 External Input, Decrementer, and Fixed Interval

Timer interrupts are enabled.

17 PR

Problem State

0 Supervisor state (privileged instructions can be

executed)

1 Problem state (privileged instructions can not be

executed)

18 FP

Floating Point Available

0 The processor cannot execute floating-point

instructions

1 The processor can execute floating-point

instructions

19 ME

Machine Check Enable

0 Machine Check interrupts are disabled

1 Machine Check interrupts are enabled.

20 FE0

Floating-point exception mode 0

0 If MSR[FE1] = 0, ignore exceptions mode; if

MSR[FE1] = 1, imprecise nonrecoverable mode

1 If MSR[FE1] = 0, imprecise recoverable mode; if

MSR[FE1] = 1, precise mode

21 DWE

Debug Wait Enable

0 Disable debug wait mode.

1 Enable debug wait mode.

22 DE

Debug interrupt Enable

0 Debug interrupts are disabled.

1 Debug interrupts are enabled.

23 FE1

Floating-point exception mode 1

0 If MSR[FE0] = 0, ignore exceptions mode; if

MSR[FE0] = 1, imprecise recoverable mode

1 If MSR[FE0] = 0, imprecise non-recoverable

mode; if MSR[FE0] = 1, precise mode

24:25 Reserved

26 IS

Instruction Address Space

0 All instruction storage accesses are directed to

address space 0 (TS = 0 in the relevant TLB

entry).

1 All instruction storage accesses are directed to

address space 1 (TS = 1 in the relevant TLB

entry).

27 DS

Data Address Space

0 All data storage accesses are directed to

address space 0 (TS = 0 in the relevant TLB

entry).

1 All data storage accesses are directed to

address space 1 (TS = 1 in the relevant TLB

entry).