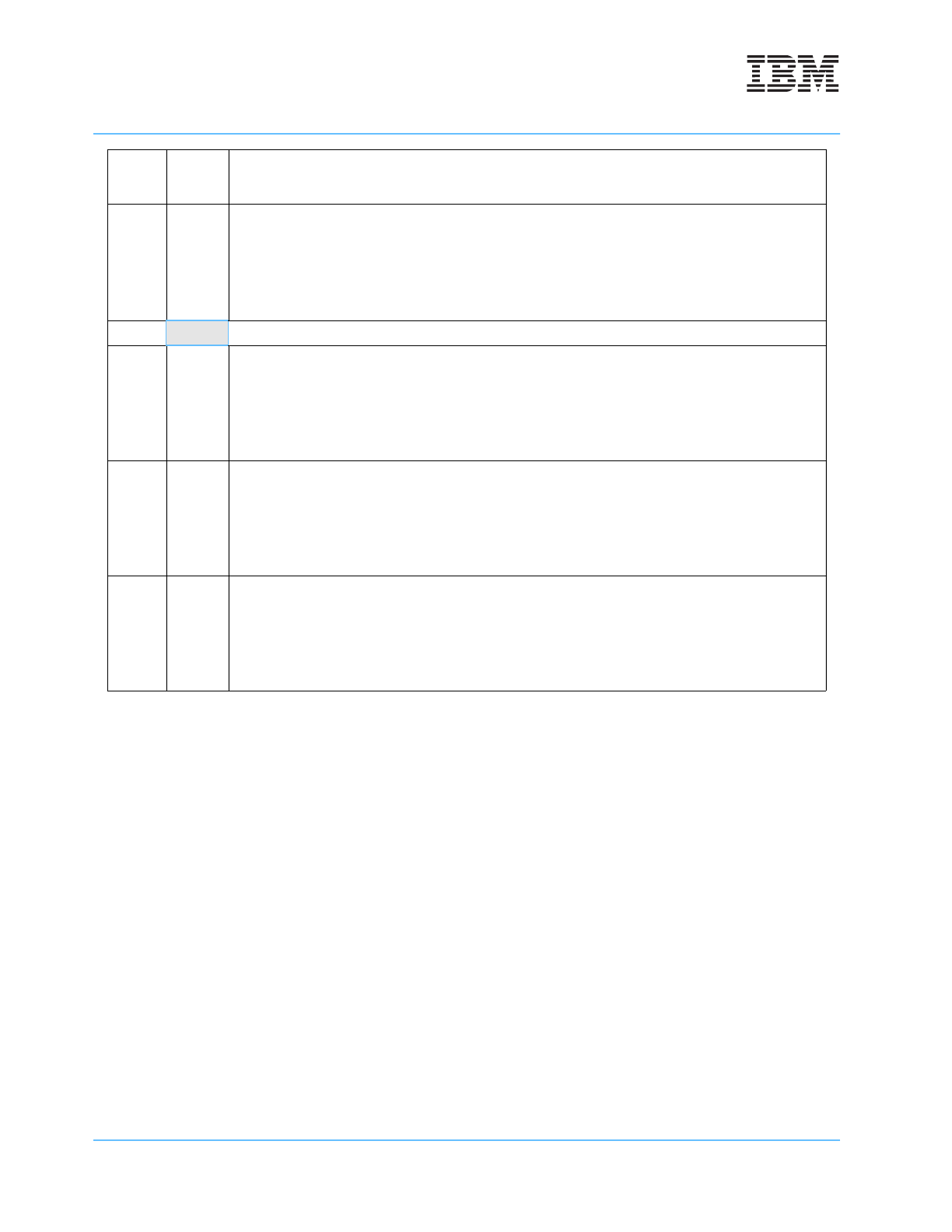

ESR (cont.)

Exception Syndrome Register

PPC440x5 CPU Core User’s Manual Preliminary

Page 488 of 589

regsumm440core.fm.

September 12, 2002

14 BO

Byte Ordering Exception

0 Byte Ordering exception did not occur.

1 Byte Ordering exception occurred.

15 PIE

Program Interrupt—Imprecise Exception

0 Exception occurred precisely; SRR0 contains

the address of the instruction that caused the

exception.

1 Exception occurred imprecisely; SRR0 contains

the address of an instruction after the one which

caused the exception.

This field is only set for a Floating-Point Enabled

exception type Program interrupt, and then only

when the interrupt occurs imprecisely due to

MSR[FE0,FE1] being set to a non-zero value when

an attached floating-point unit is already signaling

the Floating-Point Enabled exception (that is,

FPSCR[FEX] is already 1).

16:26 Reserved

27 PCRE

Program Interrupt—Condition Register Enable

0 Instruction which caused the exception is not a

floating-point CR-updating instruction.

1 Instruction which caused the exception is a

floating-point CR-updating instruction.

This is an implementation-dependent field of the

ESR and is not part of the PowerPC Book-E Archi-

tecture.

This field is only defined for a Floating-Point

Enabled exception type Program interrupt, and

then only when ESR[PIE] is 0.

28 PCMP

Program Interrupt—Compare

0 Instruction which caused the exception is not a

floating-point compare type instruction

1 Instruction which caused the exception is a

floating-point compare type instruction.

This is an implementation-dependent field of the

ESR and is not part of the PowerPC Book-E Archi-

tecture.

This field is only defined for a Floating-Point

Enabled exception type Program interrupt, and

then only when ESR[PIE] is 0.

29:31 PCRF

Program Interrupt—Condition Register Field

If ESR[PCRE]=1, this field indicates which CR field

was to be updated by the floating-point instruction

which caused the exception.

This is an implementation-dependent field of the

ESR and is not part of the PowerPC Book-E Archi-

tecture.

This field is only defined for a Floating-Point

Enabled exception type Program interrupt, and

then only when ESR[PIE] is 0.