DBCR2

Debug Control Register 2

Preliminary PPC440x5 CPU Core User’s Manual

regsumm440core.fm.

September 12, 2002 Page 473 of 589

DBCR2

SPR 0x136 Supervisor R/W

See Debug Control Register 2 (DBCR2) on page 243.

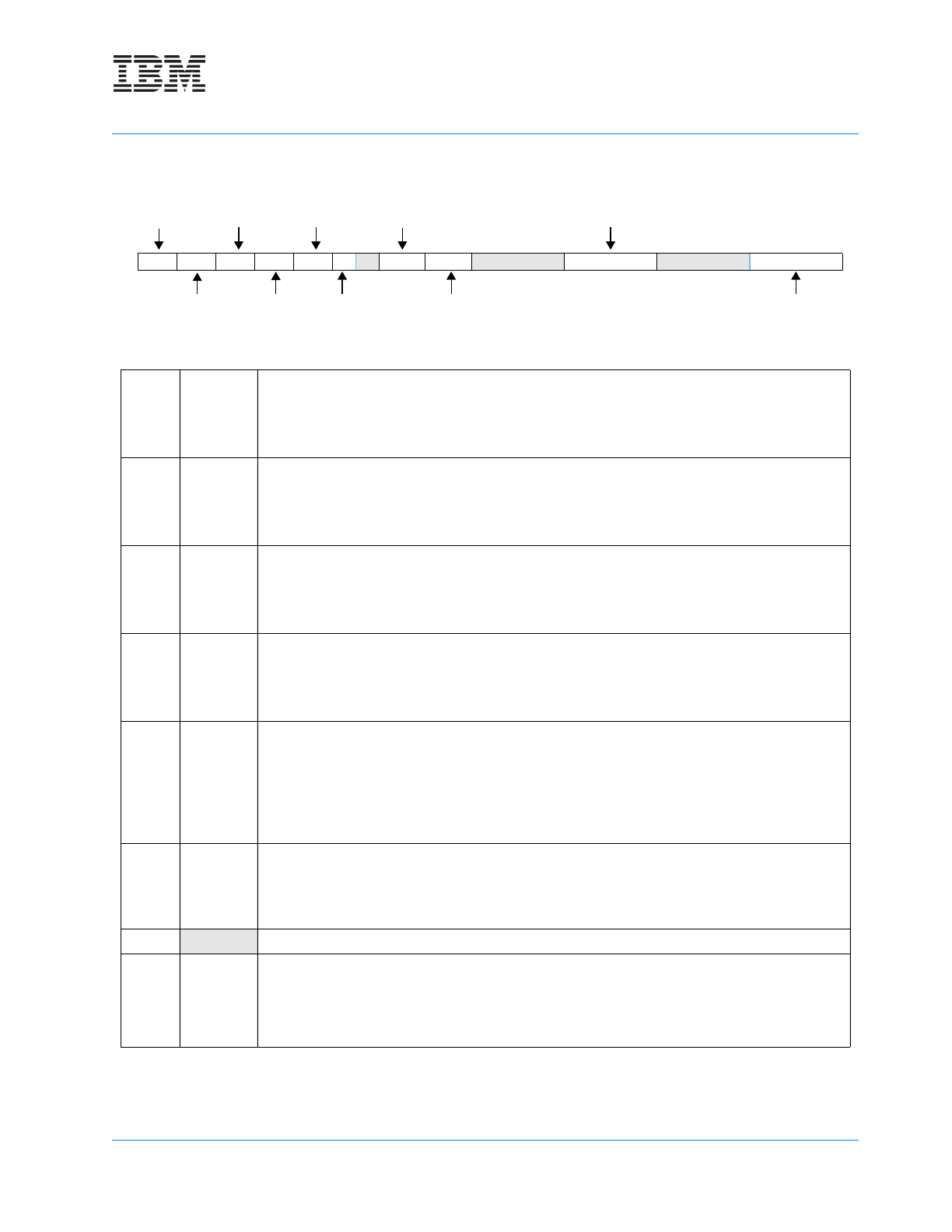

Figure 10-10. Debug Control Register 2 (DBCR2)

0:1 DAC1US

Data Address Compare (DAC) 1 User/Supervisor

00 Both

01 Reserved

10 Supervisor only (MSR[PR] = 0)

11 User only (MSR[PR] = 1)

2:3 DAC1ER

DAC 1 Effective/Real

00 Effective (MSR[DS] = don’t care)

01 Reserved

10 Virtual (MSR[DS] = 0)

11 Virtual (MSR[DS] = 1)

4:5 DAC2US

DAC 2 User/Supervisor

00 Both

01 Reserved

10 Supervisor only (MSR[PR] = 0)

11 User only (MSR[PR] = 1)

6:7 DAC2ER

DAC 2 Effective/Real

00 Effective (MSR[DS] = don’t care)

01 Reserved

10 Virtual (MSR[DS] = 0)

11 Virtual (MSR[DS] = 1)

8:9 DAC12M

DAC 1/2 Mode

00 Exact match

01 Address bit mask

10 Range inclusive

11 Range exclusive

Match if address[0:31] = DAC 1/2[0:31]; two inde-

pendent compares

Match if address = DAC1; only compare bits cor-

responding to 1 bits in DAC2

Match if DAC1 ≤ address < DAC2

Match if address < DAC1 OR address

≥ DAC2

10 DAC12A

DAC 1/2 Asynchronous

0 Debug interrupt caused by DAC1/2 exception

will be synchronous

1 Debug interrupt caused by DAC1/2 exception

will be asynchronous

11

Reserved

12:13 DVC1M

Data Value Compare (DVC) 1 Mode

00 Reserved

01 AND all bytes enabled by DVC1BE

10 OR all bytes enabled by DVC1BE

11 AND-OR pairs of bytes enabled by DVC1BE

(0 AND 1) OR (2 AND 3)

01234567891011 12 13 14 15 16 19 20 23 24 27 28 31

DAC1US

DAC1ER

DAC2US

DAC12M

DAC12A

DVC1M

DVC2BE

DVC1BE

DAC2ER

DVC2M